You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Often as we move down the process node treadmill, new challenges appear that we didn’t really have to worry about before. Often, these challenges require addressing at a number of different levels: the process, the cell libraries, the design, the EDA tools that we use.

One well known example is the problem of metal migration.… Read More

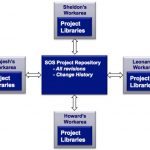

Most mixed-signal design teams don’t use data management. Well, that’s not entirely true, everyone has to do data management of some sort, it is just that it is often very ad hoc, often done by some vaguely systematic way of doing file naming, using email to keep track of changes, no access control and so on. This leads… Read More

Wally Rhines gave the keynote at DVCon yesterday. He started out with a game of “name that graph” which was unfortunately a bit spoiled since when the names were revealed the first line was off the top of the screen. But he extrapolated several trends such as the decreasing number of fabs (the current trend is that there… Read More

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

In the 1980s, Japan was seen as the leader in the semiconductor industry. Their quality was higher, especially in memories, and the US was worried about falling behind. In fact Sematech was created in 1987 by the US government and a consortium of 14 US-based semiconductor companies primarily to pool investment on common problems… Read More

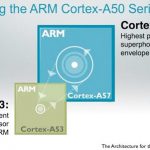

You are going to be developing software for an SoC that contains an ARM Cortex-A57 64-bit CPU. Or perhaps it is an SoC containing ARM’s hybrid big.LITTLE multi-core architecture that combines one or more low power cores with some high power, high performance cores to get the best of both worlds: high throughput when it is needed… Read More

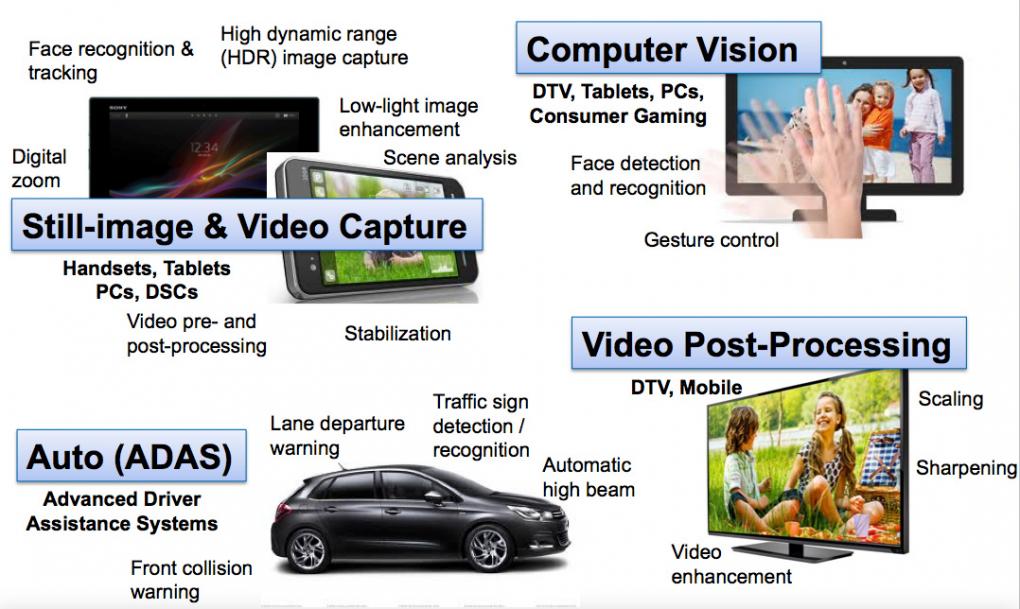

Video is a huge growing area and advanced imaging applications are becoming ubiquitous. By “advanced” I mean more than just things like cameras in your smartphone. There is lots more coming, from high-dynamic range (HDR) photography, gesture recognition, more and more intelligent video in cars to keep us safe, … Read More

Assertion Synthesis is a new tool for verification and design engineers that can be used with simulation or emulation. At DVCon Yuan Lu of Atrenta is presenting a tutorial on Atrenta’s BugScope along with John Henri Jr of Cadence explaining how it helps emulation and Baosheng Wang of AMD discussing their experiences of the… Read More

As you know, I’ve been a bit of a bear about what is happening to wafer costs at 20nm and below. At the Common Platform Technology Forum last week there were a number of people talking about this in presentations and at Harvey Jones’s “fireside chat”.

At the press lunch I asked about this. There are obviously… Read More

In July Cadence acquired Sigrity, one of the leaders in PCB and IC packaging analysis. Until a decade ago, signal integrity and power analysis was something that only IC designers needed to worry about. For all except the highest performance boards, relatively simple tools were sufficient. Provided you hooked up the pins on all… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center