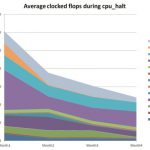

Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More

Author: Paul McLellan

Qualcomm JEDEC Mobile Keynote: Memory Bandwidth and Thermal Limits

I went to some of the JEDEC mobile conference a couple of weeks ago. The opening keynote was by Richard Wietfeld of Qualcomm called The Need for Speed.

He emphasized that smartphones are really setting the pace these days in all things mobile and internet. Over 1/3 of access is on smartphones now. Over 4/5 of searches on smartphones… Read More

Jasper Low Power Verification App

Today, Jasper announced their new Jasper-Gold Low Power Verification App. This is focused on verifying low power designs with multiple power domains, voltage islands, power shutoff, clock shutoff, and all the other techniques used for reducing power. Of course power is the main driver of SoC design these days, whether it is for… Read More

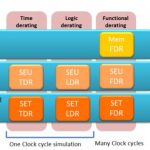

SOCFIT, Circuit Level Soft Error Analysis

I blogged recently about reliability testing with high energy neutron beams. This is good for getting basic reliability data but it is not really a useful tool for worrying about reliability while the chip is still being designed and something can be done about it.

That is where IROC Technologies SOCFIT tool comes in. It takes all… Read More

Calypto, in Three Part Harmony

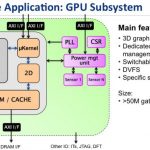

As Julius Caesar said, “Gallia est omnis divisa in partes tres.” All Gaul is divided into 3 parts. Calypto is similar with three product lines that work together to provide a system level approach to SoC design. Two of those product lines are not unique, in the sense that similar capabilities are available from a handful… Read More

Places Around the Austin Convention Center

Jerry Philippe used to work for me at Compass and then very briefly we worked together at VaST. Today he works for Calypto in Austin. And it is the Austin part that is important because Jerry knows where the places are in any city to get good food and drink but Austin is his home.

Austin has an extraordinary number of restaurants and bars.… Read More

GSA Awards…Nominate!

For 19 years GSA (presumably going back to the days when it was Fabless Semiconductor Association, FSA) has recognized public and private semiconductor companies. The awards are celebrated at a dinner. This year’s dinner is on Thursday December 12th at the Santa Clara Convention Center. The keynote speaker at the dinner… Read More

Bangers: the Best Beer Bar in Austin; Live Oak Brewing, the Best Beer in Austin

OK, enough with all this semiconductor geeky stuff. The important thing about DAC is…where to go to eat to avoid standard issue convention center chicken Caesar salad.

And a 7 minute walk from the convention center is Bangers Sausage House and Beer Gardenwhere you can have the $8 “executive” lunch consisting… Read More

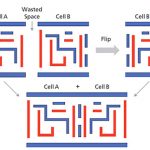

How To Design a TSMC 20nm Chip with Cadence Tools

Every process node these days has a new “gotcha” that designers need to be aware of. In some ways this has always been the case but the changes used to be gradual. But now each process node has something discontinuously different. At 20nm the big change is double patterning. At 14/16nm it is FinFET.

Rahul Deokar and John… Read More

Global Foundries Does DAC

Global Foundries will be at DAC in booth 1314. There will be 6 pods there demonstrating:

- Advanced Technology: 28nm ready and ramping, and next is 20LPM and 14XM.

- PDKs: For 28nm, 20nm and 14nm. 14nm handles FinFET enablement complexity. Robust, easy to use and high quality, supports pretty much the full range of EDA tools.

- Design

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center