You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

I met with Chris Rowen, CEO of Tensilica, last week to get his outlook on the year ahead.

He gave me an interesting quote from his time at Silicon Graphics. “We wanted to be very fast in development not to be first to market but so that we could be the last to start.”

A lot of what Tensilica does is bound up with evolving standards in audio,… Read More

I sat down yesterday with Dr. Ajoy Bose, CEO of Atrenta, to get his view of the future of EDA – looking through a high-power “spyglass” of sorts. I first met Ajoy when he was at Software & Technologies. I was then the VP of Engineering for Compass Design Automation and we were considering off-shoring some development. We eventually… Read More

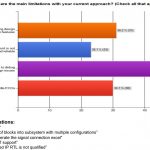

Atrenta did an online survey of their users. Of course Atrenta’s users are not necessarily completely representative of the whole marketplace so it is unclear how the results would generalize for the bigger picture, your mileage may vary. About half the people were design engineers, a quarter CAD engineers and the rest … Read More

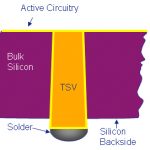

3D IC design and what has come to be known as 2½D IC design, with active die on a silicon interposer, require new approaches to verification since the through silicon vias (TSVs) and the fact that several different semiconductor processes may be involved create a new set of design challenges

The power delivery network is a challenge… Read More

Low power techniquesby Paul McLellan on 12-08-2011 at 5:49 pmCategories: General

There was recently a forum discussion about the best low power techniques. Not surprisingly we didn’t come up with a new technique nobody had ever thought of but it was an interesting discussion.

First there are the techniques that by now have become standard. If anyone wants more details on these then two good resources are… Read More

In one of those wonderfully timed coincidences, yesterday eSilicon had their partner appreciation event yesterday. They awarded the 2011 supplier of the year award to…Magma. They have been using Magma tools for almost ten years.… Read More

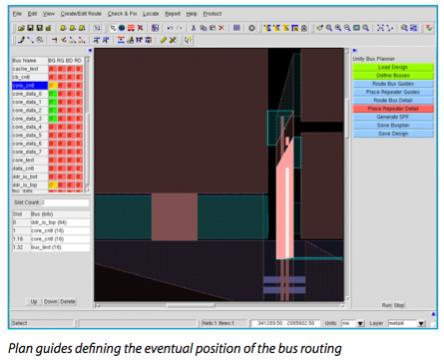

Modern microprocessor and memory designs often have hundreds of datapaths that traverse the width of the chip, many of them very wide (over one thousand signals). To meet signal timing and slope targets for these buses, designers must insert repeater cells to improve the speed of the signal. Until now, the operations associated… Read More

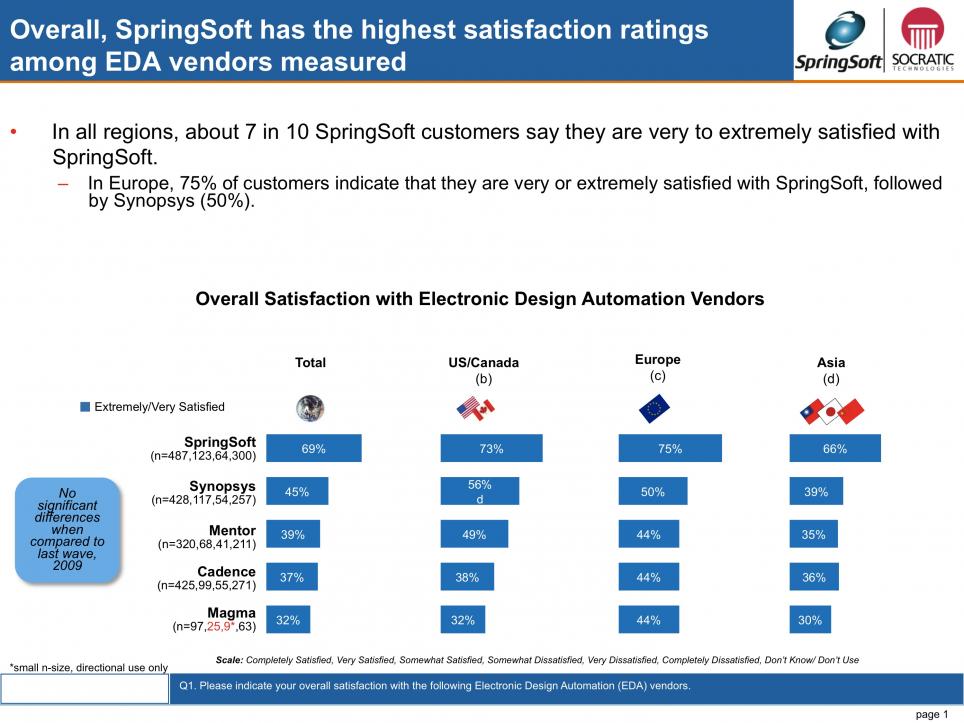

Mark Milligan recently joined SpringSoft as VP Corporate Marketing. I sat down with him on Monday to get his perspective on things.

He started life, as so many of us, as an engineer. He was an ASIC designer working on low-level microcode for the Navy Standard Airborne Computer at Control Data. It was actually the first ASIC that they… Read More

The video and slides of the CEDA lunch from a month or two ago are now (finally) up here. Chris Malachowsky presented “Watt’s next.” Chris is one of the founders of nVidia and is currently its senior VP of research. He started by talking a bit about the nVidia product line but moved on to talking about supercomputers… Read More

Earlier this week I went to the Synopsys Interoperability Forum. The big news of the day turned out to be Synopsys wanting to be more than interoperable with Magma, but that only got announced after we’d all gone away.

Philippe Margashack of ST opened, reviewing his slides from a presentation at the same forum from 10 years … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era