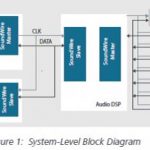

MIPI SoundWire specification will be integrated into mobiles systems, like smartphone or media tablet. In fact some of the well-known chip makers have already decided to integrate MIPI SoundWire into their last application processor release. MIPI SoundWire is also the type of specification which could be used in many other … Read More

Author: Eric Esteve

GPU Benchmarks? Try to See the Complete Picture…

We all know benchmarks, but do we really understand benchmark results? Benchmark users should always look beyond the simple score when making in-depth technical analysis and request to see all the facts. There are many graphics benchmarks to choose from but let’s name today these three below:

3DMark Ice Stormfrom Futuremark… Read More

WTL Leverage FDSOI to Achieve Both Low Power AND High Speed

In fact, this is the title of a presentation given by Pete Foley during FD-SOI Forum 2014 held in Shanghai, a couple of weeks ago. What is nice with clever people like Pete Foley is that they get the point, and get it quickly. Getting the point is to insert AND in capital in the title, as using FD-SOI technology allows to benefit from low-power… Read More

AMD Design IP Deal with Virage Logic… Oops… Synopsys

Whoever has said that history never repeats itself should read this recent PR from AMD! The news can be summarized in three points:

- Multi-year agreement gives AMD access to a range of Synopsys design IP including interface, memory compiler, logic library and analog IP for advanced FinFET process nodes

- Synopsys acquires rights

MIPI Alliance introduces C-PHY, Synopsys launch C-PHY VIP

The set of MIPI PHY specifications has enlarged during last night, as theMIPI Alliance has introduced the new C-PHY spec on September 17th, a physical layer interface for camera and display applications. “The MIPI C-PHY specification was developed to reduce the interface signaling rate to enable a wide range of high-performance… Read More

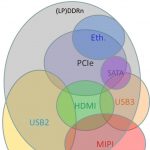

Interface IP Protocols: Status

If your company develops Design IP to support well-known protocols like USB, PCIe, HDMI, DDRn memory controller, MIPI specification (and more), it’s crucial to know your competition, the market size by segment, and even more important the market potential by segment. The latest can be obtained by the Compound Annual Growth Rate… Read More

A couple of misconceptions about FD-SOI

We have extensively discussed in Semiwiki about FD-SOI technology, explaining the main advantages (Faster, Cooler, Simpler), sometimes leading to very deep technical discussions, thanks to Semiwiki readers and their posts. I have recently found an article “Samsung & ST Team Up on 28nm FD-SOI”. This article includes many… Read More

Momentum Builds For 64-bit ARMv8-A

No doubt about it, the summer break has ended, it’s time for releasing big announcement, like this one from ARM “Momentum Builds For the Next Generation of ARM Processors”. In fact, the key information is about ARMv8-A market adoption. A total of 27 companies have signed agreements for the company’s ARMv8-A technology as… Read More

MIPS 64 bit CPU Architecture

Imagination Technologies has just launched the 5[SUP]th[/SUP] generation of MIPS CPU core, the 64-bits Warrior, or I6400 family, offering a total compatibility with the 32-bit previous architecture. MIPS Warrior I-class processor cores offers 64-bit processing in applications including embedded, mobile, digital consumer,… Read More

Why do you need 9D Sensor Fusion to support 3D orientation?

Motion sensors are also commonly applied in a broad range of consumer products, including smartphones, wearable devices, game controllers and sports watches, with applications ranging from screen orientation to indoor navigation. If you desire to build an Inertial Measurement Unit (IMU) to efficiently compute 3D orientation,… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry