By now, you’ve probably seen the news on Synopsys acquiring Coverity, and a few thoughts from our own Paul McLellan and Daniel Payne in commentary, who I respect deeply – and I’m guessing there are many like them out there in the EDA community scratching their heads a little or a lot at this. I’m not from corporate, but I am here… Read More

Author: Don Dingee

Smart cards hard for the US to figure out?

Every once in a while, I just scratch my head and wonder just what in the wide, wide world of tech is going on. More than ever, it seems the big barriers to adoption aren’t a lack of technology – instead, barriers come from a system that staunchly defends the old way of doing things, even when the participants are battered, broken, and … Read More

ISO 26262 driving away from mobile SoCs

Connected cars may be starting to resemble overgrown phones in many ways, but there are critical differences now leading processor teams in a different direction away from the ubiquitous mobile SoC architecture – in turn causing designers to reevaluate interconnect strategies.

The modern car has evolved into a microcontroller… Read More

ASTC and the new midrange ARM Mali-T720 GPU

When we last visited texture compression technology for OpenGL ES on mobile GPUs, we mentioned Squish image quality results in passing, but weren’t able to explore a key technology at the top of the results. With today’s introduction of the ARM Mali-T720 GPU IP, let’s look at the texture compression technology inside: Adaptive… Read More

Intel Quark awakening from stasis on a yet-to-be-named planet

We know the science fiction plot device from its numerous uses: in order to survive a journey of bazillions of miles across galaxies into the unknown future, astronauts are placed into cryogenic stasis. Literally frozen in time, the idea is they exit a lengthy suspension without aging, ready to go to work immediately on revival … Read More

Untangling snags earlier and reducing area by 10%

The over 20 years of experience behind Synopsys Design Compiler is getting a new look for 2014, and we had a few minutes with Priti Vijayvargiya, director of product marketing for RTL synthesis, to explore what’s in the latest version of the synthesis tool.

Previewed today, Synopsys Design Compiler 2013.12 continues to target … Read More

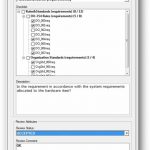

If requirements ask for it, it had better be there

Engineers are known for their attention to detail and precision in thinking, but sometimes still struggle during compliance audits. This is especially true the longer a list of requirements becomes, especially unstructured lists kept in spreadsheets and on Post-It notes.

It gets even more complicated, because in defense circles… Read More

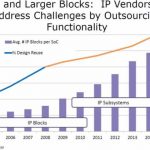

Compositions allow NoCs to connect easier

I blame it on Henry Ford, William Levitt, and the NY State Board of Regents, among others. We went through a phase with this irresistible urge to stamp out blocks of sameness, creating mass produced clones of everything from cars to houses to students.

Thank goodness, that’s pretty much over. The thinking of simplifying system design… Read More

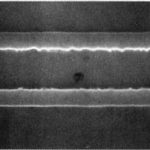

Stop TDDB from getting through peanut butter

There are a few dozen causes of semiconductor failure. Most can be lumped into one of three categories: material defects, process or workmanship issues, or environmental or operational overstress. Even when all those causes are carefully mitigated, one factor is limiting reliability more as geometries shrink – and it… Read More

Rekeying the IoT with eMTP

For non-volatile storage in IoT devices, there is technology designed to be reprogrammed many times, and technology designed to be programmed once. The many times mode is for application code, while the once mode is for keying and calibration parameters. We are about to enter the IoT rekeying zone, in between these two extremes.… Read More

Solving the EDA tool fragmentation crisis