For some time, we’ve been talking about ideas for IoT-specific chips, evolved from garden-variety MCUs or mobile SoCs. I sat in on a fascinating talk from an MCU vendor at ARM TechCon 2015 regarding multi-protocol radio silicon, and a question kept coming from the audience: what about software-defined modems? The vague response… Read More

Author: Don Dingee

More than just mobile phones for Mali

ARM TechCon 2015 was another tour de force for ARM and its ecosystem. Besides some of the developments in mobile, IoT, and security (more coming soon in the Epilogue of “Mobile Unleashed”), there were two topics that I found very educational and will cover in blogs this week. One was how the Mali family is powering more than just mobile… Read More

64-bit for the masses with Cortex-A35

It has been four years since the announcement of the ARMv8 instruction set, three years since the launch of the ARM Cortex-A57 and Cortex-A53 cores, and two years since the Apple A7 with its “Cyclone” core blew away any misunderstanding of 64-bit as being just for servers.

There is, however, still this idea that 64-bit is only for … Read More

A moment of IoT silence before we disrupt

As I sat down in the SEMI Arizona Chapter breakfast meeting a few weeks ago, a moment of semiconductor history flew right before my eyes before the IoT sessions started.

We were seated in the cafeteria of Freescale Building 94 on Elliot Road in Tempe, a place I’d been many times before, except this time may have been the last. NXP is consolidating… Read More

Pushing on AXI-connected IP in FPGAs

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More

New CoreLink IP ties in mobile GPU coherently

A mobile GPU is an expensive piece of SoC real estate in terms of footprint and power consumption, but critical to meeting user experience demands. GPU IP tuned for OpenGL ES is now a staple in high performance mobile devices, rendering polygons with shading and texture compression at impressive speeds.

Creative minds in the desktop… Read More

To err is runtime; to manage, NoC

Software abstraction is a huge benefit of a network-on-chip (NoC), but with flexibility comes the potential for runtime errors. Improper addresses and illegal commands can generate unexpected behavior. Timeouts can occur on congested paths. Security violations can arise from oblivious or malicious access attempts.

Runtime… Read More

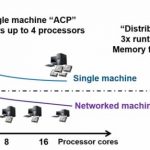

Why FPGA synthesis with Synplify is now faster

The headline of the latest Synopsys press release drops quite a tease: the newest release of Synplify delivers up to 3x faster runtime performance in FPGA synthesis. In our briefing for this post, we uncovered the surprising reason why – and it’s not found in their press release.… Read More

IoT chipsets and enterprise emulation tools

When most people talk about the IoT, it is usually all about wearables-this and low-power-that – because everyone is chasing the next huge consumer post-mobile device market. Mobile devices have provided the model. The smartphone is the on-ramp to the IoT for most consumers, with Bluetooth, Wi-Fi, and LTE, and maybe a dozen or … Read More

S2C ships UltraScale empowering SoFPGA

Most of the discussion around Xilinx UltraScale parts in FPGA-based prototyping modules has been on capacity, and that is certainly a key part of the story. Another use case is developing, one that may be even more important than simply packing a bigger design into a single part without partitioning. The real win with this technology… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era