Each quarter, the EDA Consortium publishes the Market Statistics Service (MSS) report containing detailed revenue data for the EDA industry. The report compiles data submitted confidentially by both public and private EDA companies into tables and charts listing the data by both EDA category and geographic region. This newsletter… Read More

Author: Daniel Payne

Richard Goering does Q&A with ClioSoft CEO

Richard Goering is well-known from his editorial days at EE Times (going back some 25 years), now at Cadence he blogs at least once a week on EDA topics that touch Cadence tools.

Before DAC he talked with Srinath Anantharaman about how Cadence tools work together with ClioSoft tools to keep IC Design Data Management Simple.

Through… Read More

Two More Transistor-Level Companies at DAC

In my rush on Wednesday at DAC I had almost over-looked the last two companies I talked with: Invarian and AnaGlobe. These last two I had hand-written notes on paper, so I just got to the bottom of my inbox tonight to write up the final trip reports.

Invarian

Jens Andersen and Vladimir Schellbach gave me an overview of tools that perform… Read More

Apache Design Automation acquired by Ansys

We all knew that Apache had filed for an IPO earlier and were just waiting for the timing and price to be revealed. Rumors have been circulating about an acquisition and today we know that the rumors were true asAnsys paid $310 million in cash for Apache.

Ansys stock has surged some 35% over the past twelve months:

Products

This acquisition… Read More

ARM and Mentor Team Up on Test

Introduction

Before DAC I met with Stephen Pateras, Ph.D. at Mentor Graphics, he is the Product Marketing Director in the Silicon Test Solutions group. Stephen has been at Mentor for two years and was part of the LogicVision acquisition. He was in early at LogicVision and went through their IPO, before that he was at IBM in the mainframe… Read More

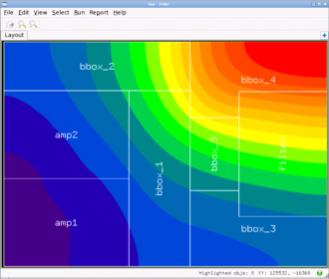

Circuit Simulation and IC Layout update from Mentor at DAC

Intro

On Monday evening I talked with Linda Fosler, Director of marketing for the DSM Division at Mentor about what’s new at DAC this year in circuit simulation and IC layout tools.

Notes

IC Station – old name for IC layout tools

Eldo – Eldo Classic- Cell characterization

– ST is the early customer and teaching customer,… Read More

DRC tool guns for Calibre at DAC

Intro

Across the aisle from the Mentor booth at DAC sat a DRC tool competitor to Calibre. I received an update from Randy Smith of Polyteda on Wednesday afternoon, my last EDA vendor of the week.

Ravi Ravikumar, Randy Smith

Notes

Randy Smith – CEO (February 2011) [former founder is gone]- 1979 at HP developing internal tools

–… Read More

An Affordable 3D Field Solver at DAC

Intro

Massimo Sivilotti, Ph.D of Tanner EDA showed me their 3D field solver in the HiPer PX extraction tool at DAC last week.

Notes

Tool Suites – schematics, layout, SPICE simulation, DRC/LVS

– HiPer PX: 3D Field solvero Layers, dielectrics,

o Finite element analysis

o Boundary element methods

o 2D mode for pattern matching… Read More

Hardware Configuration Management at DAC

Intro

Show me what has changed in my RTL or Schematic since the last time I looked. This task is now automated by Cliosoft with their new hierarchical tool called Visual Design Difference (VDD). Srinath showed me what was new for DAC.

Srinath Anantharaman

Notes

LSI, STMicro – use DesignSync for their DM but use VDD for seeing visual… Read More

Circuit Simulation update from Cadence at DAC

Intro

In the bloggers suite I met with John Pierce of Cadence last Wednesday to get an update on what’s new with circuit simulation at DAC this year.

Notes

News – market is growing, RF CMOS simulation is growing

– Show on RF (MTT – Microwave Technology ) this week, sharing a booth with AWR this week

– Recent news with… Read More

Disaggregating LLM Inference: Inside the SambaNova Intel Heterogeneous Compute Blueprint