My engineering background includes designing at the transistor-level, so I was drawn to attend a webinar today presented by Tanner EDAand Incentia about Adding a Digital Block to an Analog Design. Many of the 30,000 users of Tanner tools have been doing AMS designs, so adding logic synthesis and static timing analysis from Incentia… Read More

Author: Daniel Payne

Two New Announcements at ITC from Synopsys

Each year at the International Test Conference(ITC) we hear about the latest advances from the testability side of both EDA vendors and academics. This year Aart de Geus, Chairman and Co-CEO of Synopsys delivered a keynote speech titled, “Testing Positive, for Complexity“. Yesterday I spoke with Robert Ruiz and… Read More

Power Management Policies for Android Devices

I’ll never forget the shock when I upgraded from a Feature Phone to my first Android-powered SmartPhone, because all of a sudden my battery life went from 6 days down to only 1 day between charges. As a consumer, I really want my battery to last much longer than one day, so the race is on for mobile phone companies to design their… Read More

Recap of the Apple iPad Announcement

I watched the live stream product announcements yesterday from Apple and will give you a quick recap of what I gleaned. First off, Apple live stream requires that you use the Safari browser, so that meant that I couldn’t use Google Chrome, so much for adopting web standards.

Apple Products Talked about

iPhone 6 and 6 Plus

This… Read More

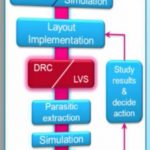

Finding Logic Issues Early that Impact Physical Implementation

Complex SoC project teams typically use a divide and conquer approach where specialized engineers work in separate domains, like front-end or back-end. The five major engineering tasks for IC design can be described as: RTL design, synthesis, floor planning, place and route, then finally design analysis.

What if you could detect… Read More

How ST Designs with Layout Dependent Effects (LDE)

I first visited STat their Agrate, Italy site where Flash memory development is done. At DACthis year Antonio Bogani talked about how ST designs with LDE while using EDA tools and a PDK (Process Design Kit) from Cadence. They recorded the 17 minute presentation, and you can view it herewithout having to register. Antonio’s… Read More

Full-Chip Electromigration Analysis

I’ll never forget debugging my first DRAM chip at Intel, peering into a microscope and watching the aluminum interconnect actually bubble and dissolve as the voltage was increased, revealing the destructive effects of Electromigration (EM) failure. That was back in 1980 using 6 um, single level metal technology, so imagine… Read More

IP and Design Management Done Right

At DACin San Francisco this past June I was able to visit and blog about two dozen EDA companies, however there were so many more products and events to see that I couldn’t possibly have enough time to enjoy them all. Fortunately for me there were plenty of videos made of vendor presentations, so this week I got caught up a bit by… Read More

Designing SmartCar ICs

When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

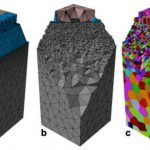

SiC and Si Power Devices

ICs for consumer electronics are often battery powered, which are considered low voltage designs. On the other end of the IC spectrum are high voltage devices used in many industrial applications like: automotive, aerospace, data centers, transportation and power generation. … Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem