There’s much talk in EDA about High Level Synthesis (HLS), Transaction Level Modeling (TLM) and the Universal Verification Methodology (UVM), however there’s a lower-level of abstraction, the transistor-level, where high-speed digital cell libraries are created, analog circuits are crafted, and AMS designers… Read More

Author: Daniel Payne

Leakage Current TCAD Calibration in a-Si TFTs

Two weeks ago I blogged about amorphous silicon and how that material is well-suited for designing TFTs. Today I’m following up after watching the archived webinarpresented by Nam-Kyun Tak of Silvaco. After clicking on that link you’ll be brought to a brief sign-up page and then can watch the archived webinar in your… Read More

Simulation and Analysis of Power and Thermal Management Policies

Earlier this month I blogged about Power Management Policies for Android Devices, so this blog is part two in the series and delves into the details of using ESL-level tools for simulation and analysis. The motivation behind all of this is to optimize a power management system during the early design phase, instead of waiting until… Read More

Using Cadence PVS for Signoff at TowerJazz

TowerJazzis a specialty foundry that provides IC manufacturing into several markets, like: RF, high-performance analog, power, imaging, consumer, automotive, medical, industrial and aerospace/defense. In June there was a presentation from Ofer Tamir of TowerJazz at DACin the Cadence theatre, so I had a chance this week … Read More

Power-Aware Verification in Mixed-Signal Simulation

My Samsung Galaxy Note 2 phone lasts about 1.5 days on a single battery charge, thanks in part to the clever power conservation approaches like when the screen is automatically dimmed then turned off after no activity. Mobile phones and many other battery-powered devices used today all need power-saving designs, which then means… Read More

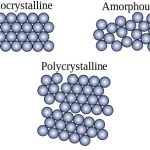

Amorphous Silicon and TFTs

Most ICs are fabricated with crystalline silicon (c-Si), which is a tetrahedral structure forming a well-ordered crystal lattice. There’s another form of semiconductor material called amorphous silicon (a-Si) which has no long-range periodic order. It turns out that a-Si is a great material for the active layer in thin-film… Read More

Daylight Savings Time and the IoT

On Sunday in the USA we changed our clocks back one hour to account for Daylight Savings Time and I was reminded of how far we have to go in getting all of our devices to understand and automatically account for the time. Despite all of the talk about IoT and how it has the promise to automate our lives, we still have to manually set the time.… Read More

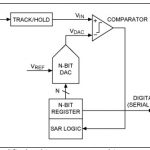

Debugging a 10 bit SAR ADC

SMIC (Semiconductor Manufacturing International Corporation) is a China-based foundry with technology ranging from 0.35 micron to 28 nm, and we’ve blogged about them before on SemiWiki. I’ve been reading about SMIC recently because they created a technical presentation for the MunEDA Technical Forum Shanghai… Read More

Silvaco at the TSMC 2014 Open Innovation Platform

The success of our semiconductor eco-system depends on collaboration, so the annual TSMC OIP Event just held on September 30 at the San Jose Convention Center was a prime example of that. I didn’t attend this year, but I did follow up with Amit Nandaof Silvaco this week to hear about what they presented. As a consultant I’ve… Read More

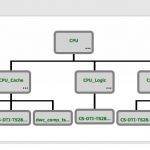

Effective Bug Tracking with IP Sub-systems

Designing an SoC sounds way more exciting than bug tracking, but let’s face it – any bug has the potential to make your silicon fail, so we need to take a serious look at the approaches to bug tracking. When using an IP or an IP subsystem in a design, the SoC integrators require some critical knowledge about this IP. The actual… Read More

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem