You may be under the impression that anything to do with neural nets necessarily runs on a GPU. After all, NVIDIA dominates a lot of what we hear in this area, and rightly so. In neural net training, their solutions are well established. However, GPUs tend to consume a lot of power and are not necessarily optimal in inference performance… Read More

Author: Bernard Murphy

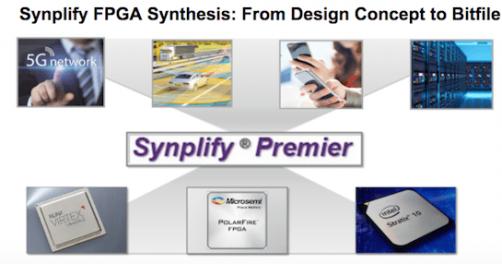

Webinar: Optimizing QoR for FPGA Design

You might wonder why, in FPGA design, you would go beyond simply using the design tools provided by the FPGA vendor (e.g. Xilinx, Intel/Altera and Microsemi). After all, they know their hardware platform better than anyone else, and they’re pretty good at design software too. But there’s one thing none of these providers want to… Read More

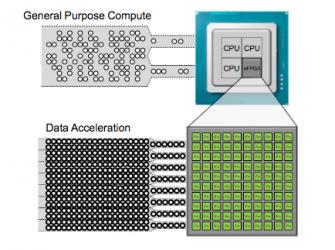

Accelerating Accelerators

Accelerating compute-intensive software functions by moving them into hardware has a long history, stretching back (as far as I remember) to floating-point co-processors. Modern SoCs are stuffed with these applications, from signal processors, to graphics processors, codecs and many more functions. All of these accelerators… Read More

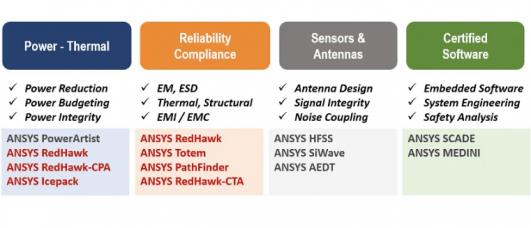

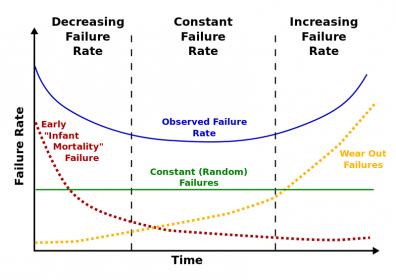

Reliability Signoff for FinFET Designs

Ansys recently hosted a webinar on reliability signoff for FinFET-based designs, spanning thermal, EM, ESD, EMC and aging effects. I doubt you’re going to easily find a more comprehensive coverage of reliability impact and analysis solutions. If you care about reliability in FinFET designs, you might want to check out this webinar.… Read More

Magillem User Group Meeting

Magillem is hosting a user group meeting on October 26th at The Pad in Sunnyvale. User Group meetings are always educational; this one should be especially so for a number of reasons, not least of which is the keynote topic: Expert Systems for Experts.

REGISTER HERE for the meeting in Sunnyvale on October 26[SUP]th[/SUP] from 10:00am… Read More

TechCon: See ANSYS and TSMC co-present

ANSYS and TSMC will be co-presenting at ARM TechCon on Multiphysics Reliability Signoff for Next Generation Automotive Electronics Systems. The event is on Thursday October 26th, 10:30am-11:20am in Grand Ballroom B.

You can get a free Expo pass which will give you access to this event HERE and see the session page for the event … Read More

An IIot Gateway to the Cloud

A piece of learning we all seem to have gained from practical considerations of IoT infrastructure is that no, it doesn’t make sense to ship all the data from an IoT edge device to the cloud and let the cloud do all the computational heavy lifting. On the face of it that idea seemed good – all those edge devices could be super cheap (silicon… Read More

An Informal Update

I mentioned back in June that Synopsys had launched a blog on formal verification, intended to demystify the field and provide help in understanding key concepts. It’s been a few months, time to check in on some of their more recent posts.

First up, it feels like they are finding their groove. Relaxed style, useful topics but now with… Read More

Adoption, Architecture and Origami

Last week I sat in on Oski’s latest in a series of “Decoding Formal” sessions. Judging by my first experience, they plan and manage these events very well. Not too long (~3 hours of talks), good food (DishDash), good customer content, a good forward-looking topic and a very entertaining wrap-up talk.… Read More

High-Speed Equivalence Checking

Following on product introductions for simulation and prototyping, physical verification and implementation earlier in the year, Anirudh Devgan (Exec VP and GM at Cadence), the king of speed and parallelism has done it again, this time with logic equivalence checking (LEC). Cadence recently announced an advance to their well-known… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea