Scanning ACM tech news recently, I came across a piece that spoke to my inner nerd; I hope it will appeal to some of you also. The discovery will have no impact on markets or investments or probably anyone outside theories of machine learning. Its appeal is simply in the beauty of connecting a profound but obscure corner of mathematical… Read More

Author: Bernard Murphy

Why High-End ML Hardware Goes Custom

In a hand-waving way it’s easy to answer why any hardware goes custom (ASIC): faster, lower power, more opportunity for differentiation, sometimes cost though price isn’t always a primary factor. But I wanted to do a bit better than hand-waving, especially because these ML hardware architectures can become pretty exotic, so … Read More

Contrarian Views on Quantum Computing

I’m not opposed to the exotic ideas which capture public attention from time to time, but I do enjoy puncturing a popular expectation demanding every novel technology be a revolutionary breakthrough. I’ve already made my small contribution to driving a stake through the heart of claims that quantum computing (QC) will replace… Read More

A Sharper Front-End to Intelligent Vision

In all the enthusiasm around machine learning (ML) and intelligent vision, we tend to forget the front-end of this process. The image captured on a CCD camera goes through some very sophisticated image processing before ML even gets to work on it. The devices/IPs that do this are called image signal processors (ISPs). You might … Read More

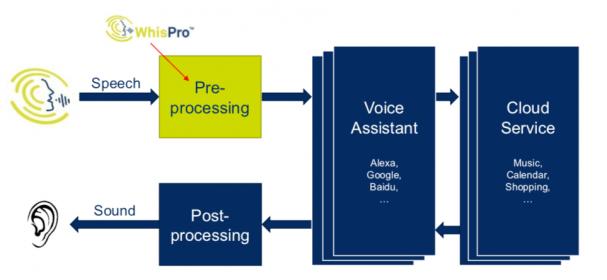

WhisPro: A Speech Recognition Option from CEVA

In the superheated world of AI and Neural Nets (NN), many of us are familiar with object recognition in images: cars, pedestrians, cats and dogs and thousands of other applications. But there’s another class of applications, also growing rapidly, around audio AI. Early generations for command recognition in infotainment systems… Read More

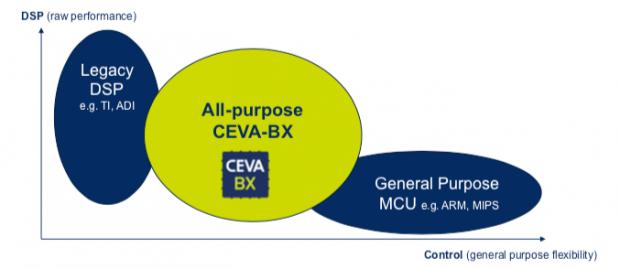

CEVA-BX: A Hybrid DSP and Controller

I’ve noticed hybrid solutions popping up recently (I’m reminded of NXP’s crossover MCU released in 2017). These are generally a fairly clear indicator that market needs are shifting; what once could be solved with an application processor or controller or DSP or whatever, now needs two (or more) of these. In performance/power/price-sensitive… Read More

Disturbances in the AI Force

In the normal evolution of specialized hardware IP functions, initial implementations start in academic research or R&D in big semiconductor companies, motivating new ventures specializing in functions of that type, who then either build critical mass to make it as a chip or IP supplier (such as Mobileye – intially)… Read More

Ampere: More on Arm-Based Servers

Since I talked recently about AWS adding access to Arm-based server instances in their cloud offering, I thought it would be interesting to look further into other Arm-based server solutions. I had a meeting with Ampere Computing at Arm TechCon. They offer server devices and are worth closer examination as a player in this game.… Read More

Big Data Analytics in Early Power Planning

ANSYS recently hosted a webinar talking about how they used the big-data analytics available in RedHawk-SC to do early power grid planning with static analytics, providing better coverage than would have been possible through pure simulation-based approaches. The paradox here is that late-stage analysis of voltage drops … Read More

ARM Answers Server Doubts

At ARM TechCon this year, the company announced the Neoverse brand targeted to infrastructure, contrasting with the Cortex brand we are familiar with for edge devices such as smartphones and IoT devices. Cortex was already used in infrastructure, in networking, base stations and the like but Neoverse splits the infrastructure… Read More

Solving the EDA tool fragmentation crisis