TSMC, the world’s most trusted semiconductor foundry, released its 2024 Sustainability Report, underscoring its commitment to embedding environmental, social, and governance principles into its operations. Founded in 1987 and headquartered in Hsinchu Science Park, TSMC employs 84,512 people globally and operates… Read More

TSMC 2025 Update: Riding the AI Wave Amid Global Expansion

Welcome to the second half of a very exciting year in semiconductors. While Intel and Samsung Foundry have made quite a few headlines, TSMC continues to execute flawlessly at 3nm and 2nm. With the TSMC OIP Ecosystem Forums starting later this month let’s take a look at how we got to where we are today.

Alchip Launches 2nm Design Platform for HPC and AI ASICs, Eyes TSMC N2 and A16 Roadmap

Alchip Technologies, a global leader in high-performance computing (HPC) and AI infrastructure ASICs, has officially launched its 2nm Design Platform, marking a major advancement in custom silicon design. The company has already received its first 2nm wafers and is collaborating with customers on the development of high-performance… Read More

Certus Semiconductor at the 2025 Design Automation Conference #62DAC

Certus Semiconductor Brings High-Performance Custom I/O and ESD IP to DAC 2025

Certus Semiconductor, a trusted leader in custom I/O and ESD solutions, will exhibit at booth #1731 during DAC 2025, June 23–27 in San Francisco. Known for its robust, customer-proven IP tailored for challenging applications, Certus will highlight… Read More

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

Analog Bits Steals the Show with Working IP on TSMC 3nm and 2nm and a New Design Strategy

The TSMC Technology Symposium recently kicked off in Santa Clara, with a series of events scheduled around the world. This event showcases the latest TSMC technology. It is also an opportunity for TSMC’s vast ecosystem to demonstrate commercial application on TSMC’s technology. There is a lot to unpack at an event like this. There… Read More

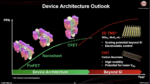

TSMC Describes Technology Innovation Beyond A14

The inaugural event for the 2025 TSMC Technology Symposium recently concluded in Santa Clara, California. This will be followed by events around the world over the next two months. We have summarized information from this event regarding process technology innovation and advanced packaging innovation. Overall, the A14 process… Read More

TSMC Brings Packaging Center Stage with Silicon

The worldwide TSMC 2025 Technology Symposium recently kicked off with the first event in Santa Clara, California. These events typically focus on TSMC’s process technology and vast ecosystem. These items were certainly a focus for this year’s event as well. But there is now an additional item that shares the spotlight – packaging… Read More

TSMC 2025 Technical Symposium Briefing

At the pre-conference briefing, Dr. Kevin Zhang gave quite a few of us media types an overview of what will be highlighted at the 2025 TSMC Technical Symposium here in Silicon Valley. Since most of the semiconductor media are not local this was a very nice thing to do. I will be at the conference and will write more tomorrow after the … Read More

IEDM 2025 – TSMC 2nm Process Disclosure – How Does it Measure Up?

Initial thoughts

At IEDM held in December 2024, TSMC presented: “2nm Platform Technology featuring Energy-efficient Nanosheet Transistors and Interconnects co-optimized with 3DIC for AI, HPC and Mobile SoC Applications,” the authors are:

Geoffrey Yeap, S.S. Lin, H.L. Shang, H.C. Lin, Y.C. Peng, M. Wang, PW Wang, CP Lin, KF… Read More