“Simulation: Expert Insights into Modeling Microcontrollers” was the recent panel hot topic at Renesas DevCon2012, featuring Paolo Giustoof GM, Mark Ramseyerof Renesas, Marc Serughettiof Synopsys, Jay Yantchevof ASTC / VWorks, and Simon Davidmannof Imperas.

Continue reading “Simulation: Expert Insights into Modeling Microcontrollers @ Renesas DevCon”

SoC emulation syncs up with SuperSpeed USB

They say what adds value is to take something difficult and make it look simple. USB looks so simple when it is done right, but designers know it can be one of the more tempermental features in an SoC, especially in the latest SuperSpeed incarnation.

Continue reading “SoC emulation syncs up with SuperSpeed USB”

A Brief History of Today’s Flexible ASIC Model

There’s been an interesting trend emerging the past couple of years; a gentrification, if you will, of the ASIC business. What was thought to be a dying supply chain model has re-emerged as a health and growing segment of the semiconductor industry. Recent figures from Gartner place 2012 ASIC revenue at around $24.4 billion on a growth rate of approximately 8%. Over the next five years, Gartner expects the ASIC segment to grow at compounded annual growth rate (CAGR) of 7.6%, outstripping the CAGR of ASSP’s at 4% and the semiconductor industry as whole at around 4.9%.

I’ve taken this “back to the future” retrospective because the health of today’s ASIC business is rooted in the history of the fabless semiconductor industry.

In the first article of this series, I sited how, in the early 1980’s, integrated device manufacturers — some of them the successful ASIC companies of their time — sold off their excess capacity to their poorer cousins, the start-up (read fabless) semiconductor companies who could not yet afford their own manufacturing capabilities. Then of course, Dr. Morris Chang brought TSMC to market in 1987, providing capacity and manufacturing technology for all comers and introduced the dedicate foundry model that really broke open semiconductor innovation.

Interestingly, Dr. Chang’s vision ushered in not only the semiconductor foundry but also the semiconductor fabless model, the semiconductor third party IP model, and today’s regenerated ASIC business.

One of these new ASIC companies, Global Unichip Corp., now known as GUC, started in 1998, 11 short years after TSMC first opened its doors and about the same time that the foundry industry gained recognition as a sustainable, viable model. The company was founded by a trio of some of the more influential luminaries of the Taiwan semiconductor. The group included Dr. Nicky Lu, IEEE Fellow and the Founder and Chairman of Etron, Dr. Y.L. Lin, a Professor at National Tsinghua University, and K.C. Shih, Founder and Board Member. Even back then, the founders recognized that the semiconductor industry was getting more and more complex and that system houses and fabless companies would not be able to manage the whole value chain.

Mr. Shih referred to his new company as a “design service company” because, at the time, design was the point of greatest complexity. In 2003, TSMC saw the complexity conundrum from the foundry perspective and gave credence to the emerging segment when they became a significant shareholder in GUC. Soon, other companies entered the space. Open Silicon, eSilicon and later Socle provided industry validation.

Growing semiconductor complexity, the demand for increased supply chain efficiency and the risk of costly product failures continued to erect significant barriers to innovation for the fabless, IDM and system house segments and created opportunity for the emerging Design Service companies who began to expand beyond their initial core competencies and into IP customization, test and packing and, in some cases, sophisticated logistics management.

Soon IDM’s began going “fab lite” as they transitioned beyond their process technology differentiation and it became obvious that foundry-partnered design service supply chains might be a better alternative. At the same time, systems houses began to insist on increased differentiation that could only be achieved through domain know-how, IP availability and, interestingly, a return to vertical integration. The confluence of these factors created the need for companies that provided capabilities well beyond design. Success, it became obvious, would come by providing a broad portfolio of “virtual” supply chain (or ASIC) services that could be accessed by individual companies at individual points of entry based upon their specific strengths and their specific needs. And so in 2011, GUC began providing this integrated service set under the banner of its Flexible ASIC Model[SUP](TM)[/SUP][SUB].[/SUB]

Today, GUC’s Flexible ASIC Model covers three integrated supply chain areas: SoC integration, implementation methodologies and integrated manufacturing. Taken together, they bring today’s systems houses, IDMs and fabless semiconductor companies access to a foundry design environment that reduces cycle time, IP and design methodologies that lower the barriers to innovation and integrated technology availability (design, foundry, assembly and test) that speeds time-to-market.

Interesting, the trends that emerge from development of the fabless semiconductor industry continue today and the maturation of Flexible ASIC model appears to be just the next stage in the history of continued semiconductor innovation.

Brian Bailey Interviews Kathryn Kranen

Brian Bailey at EETimes has an interesting interview with Kathryn Kranen. He says that the interview will be published in installments but the first one is up here. This first installment is mostly about how long-lived EDA companies (and others) have become since it takes a long time to build up enough revenue to be able to IPO.

She contrasts how she has worked at Jasper and earlier companies with Jim Hogan’s “run lean, don’t raise too much money” approach. Each time she raised over $30M. Her view is that small companies don’t scale for success. If a company with hundreds of designers adopts a product from and EDA company then the EDA company has to be of a scale to handle that, international offices, lots of AEs and so on. A small company can develop some technology and establish some level of credibility but then it has to be acquired by a company with a large channel to scale.

Go read the whole thing.

Model Driven Development

Mentor has a webinar on Model Driven Development (MDD) for Systems Engineering, presented by Bill Chown. It is actually the first of 15 webinars. This first one is just over 30 minutes long and I assume the others will be too. The webinar focuses on embedded system development, which historically has largely been validated using physical prototypes. Of course one problem with that is that by the time you get to physical prototypes it is hard to make major architectural changes. If the hardware is a chip, by the time you have a prototype it is almost impossible to make any changes at all.

UML (which stands for Universal Modeling Language) is a very general purpose modeling language orignally used mostly for object-oriented software development. Developed originally in the mid-90s it has been extended to hardware development and, especially, systems that consist of lots of components perhaps in different domains: hardware, software, mechanical and so on.

The idea of model driven development is to use UML at the architectural stage and so instead of ending up with requirements on reams of paper and a few spreadsheets there is an executable specification. This can be made use of through the whole development cycle by:

- architect

- component developers

- system integrators

BridgePoint consists of 3 major components:

[LIST=1]

Mentor plans to make the UML editor open-source, but the Verifier and Model Compilers will remain Mentor products.

The Model Driven Development webinar is here.

There are also short 5-minute tutorials on various aspects of UML and Mentor’s BridgePoint here.

The next webinar is on October 30th at 8am. Bill Chown will present UML, xtUML and the xtUML Process. Registration is here.

The remaining webinars (through next February) are:

- Creating an xtUML Model (Part 1: The Diagrams) Nov 6, 2012

- Creating an xtUML Model (Part 2 – Object Action Language) Nov 13, 2012

- xtUML and Domain-specific Modeling Nov 20, 2012

- Verification and Validation of xtUML Models Nov 27, 2012

- Model Compilation Dec 4, 2012

- xtUML Projects with Legacy Code Dec 11, 2012

- SystemC Virtual Platform Creation Dec 18, 2012

- Executable Testbench Design in xtUML Jan 8, 2013

- xtUML and the Notion of Time Jan 15, 2013

- Best Practices for Structuring an xtUML Project Jan 22, 2013

- Configuration Management in xtUML Projects Jan 29, 2013

- Safety-critical Applications and xtUML Feb 5, 2013

- Customizing a Model Compiler Feb 12, 2013

A Brief History of Semiconductors

In the last few decades, electronics has become more and more central to our lives. When I was a child the only electronics in the house was the radio and the television, both of which contained tubes. Two big things happened that upended that world: the invention of the transistor and the invention of the integrated circuit. A modern integrated circuit, or chip as some people like to call them, may have over a billion transistors on it and yet sell for just a few dollars. Perhaps more surprising, every one of those transistors works correctly.

As a result, today our cell phones have more power than the supercomputers of yesteryear. Our cars contain dozens of microprocessors. We shop online. We read books on our Kindles or iPads. We play videogames on consoles that are more powerful than the flight simulators of twenty years ago.

Like the comedian who rehearses intensely until it all looks ad-libbed, as it turns out it is really expensive to make electronics that cheap. Chips are built in factories known as fabs (actually short for fabrication line). Fabs cost more than nuclear power plants. They are filled with specialized machines costing tens of millions of dollars each. Chips are designed by teams of hundreds of design engineers and they are surrounded by an ecosystem of specialized software that sells for tens if not hundreds of thousands of dollars per copy without which these chips wouldn’t be possible.

Designing a chip and getting it manufactured is a bit like the pharmaceutical industry. Getting to the stage that a drug can be shipped to your local pharmacy is enormously expensive but when you are done you have something that can be manufactured for a few cents and sold for, perhaps, ten dollars. A chip is like that (although for different reasons). Getting a chip designed and manufactured is incredibly expensive, but when you are done you have something that can be manufactured for a few dollars and enable products that can be sold for hundreds of dollars. The first chip may cost millions of dollars but you can make hundreds of millions of dollars if you sell a lot of them.

So let’s go back to the beginning:

The transistor was invented at Bell Labs in New Jersey in 1947 by John Bardeen, Walter Brattain and William Shockley. The transistor is at the heart of almost all electronics and so it is one of the most important inventions of the 20[SUP]th[/SUP] century. Shockley fell out of favor with Bell Labs and returned to Palo Alto where he had been brought up. He opened the Shockley Semiconductor Laboratory of Beckman Instruments and tried to lure ex-colleagues from Bell Labs to join him. When he was unsuccessful, he searched universities for the brightest young graduates to build the new company. This was truly the genesis of Silicon Valley and some of its culture that still exists today. Shockley is credited with bringing the silicon to Silicon Valley.

Shockley’s management style was abrasive and caused dissension in the ranks but the final straw was when Shockley decided to discontinue research into silicon-based transistors. Eight people, known as the traitorous eight, resigned and with seed money from Fairchild Camera and Instrument they created Fairchild Semiconductor Company. Almost all semiconductor companies, especially Intel, AMD and National Semiconductor (now part of Texas Instruments), have their roots in Fairchild in one way or another. It was where silicon based integrated circuits began, which as it turns out, is the prevailing technology still in use today.

The second big step, the invention of the integrated circuit, took place simultaneously at Fairchild and Texas Instruments from 1957 to 1959. Jean Hoerni at Fairchild developed the planar transistor then Jack Kilby at Texas Instruments and Robert Noyce at Fairchild developed the integrated circuit.

This turned out to be the big breakthrough. Until that point transistors were built one at a time and wired together manually. The planar manufacturing process allowed multiple transistors to be created simultaneously and connected together simultaneously. By 1962 Fairchild was producing integrated circuits with about a dozen transistors. Much has changed in the intervening years but this same basic principle is how we build today’s chips with billions of transistors.

So those two inventions, the transistor and the integrated circuit, really are the key to electronics today and the ways in which semiconductors affects our lives.

A Brief History of Semiconductors

A Brief History of Moore’s Law

A Brief History of ASICs

A Brief History of Programmable Devices

A Brief History of the Fabless Semiconductor Industry

A Brief History of TSMC

A Brief History of EDA

A Brief History of Semiconductor IP

A Brief History of SoCs

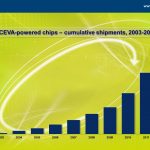

4 Billion CEVA powered Chips shipped

Why making the difference between chips and cores, when mentioning that CEVA’s customers have shipped four billion IC to date? Because that can make a big difference! Imagine for example an IP vendor selling processor IP cores to be used in massively parallel computing application, when the chip maker create a processor NxM matrix, where every IP core is duplicated (N x M) times… When you ship one chip, you also ship N x M cores.

In the SC industry, we evaluate a market made of IC shipments, and even if an IP is instantiated multiple times in the same chip, at the end of the day, we just count the shipment of such a chip – called “unit” – to calculate a market share. If anybody prefers to start counting IP cores, I strongly suspect that the standard cell Library vendors will end up winning the game…

Let’s come back to the exponential growth of units shipped by CEVA’ customers. What kind of application has allowed such a growth during the last couple of years? I am sure you guess it, and you are right: smartphone! But not only, as CEVA DSPs have now powered audio/voice in more than 2 billion devices, including many of the world’s leading gaming console, set-top-box, DTV, home audio devices… and smartphone. When looking at CEVA’s customer list, many of the world’s leading electronics brands, including; HTC, Huawei, Lenovo, LG, Motorola, Nintendo, Panasonic, Philips, Samsung, Sanyo, Sharp, Sony, Toshiba and ZTE are represented. Just like with ARM processor core, CEVA DSP IP core have been first implemented in the wireless segment, to run the baseband processing (for the DSP) and the application processing (starting with ARM7 in the 90’s, up to ARM CortexA9 double core today), and these IP cores are now used in various market segments.

Listening to Will Strauss, President of Forward Concepts, help understanding the winning strategy: “I congratulate CEVA for its monumental achievement of reaching 4 billion CEVA-powered chips shipped. It affirms CEVA’s clear market share lead in DSP IP and is a testament to its dedicated customer base. In recent years, CEVA has re-defined the classical DSP architecture by introducing special purpose DSPs such as the CEVA-XC that enable software-based modems and a unified platform for LTE, LTE-Advanced 802.11ac and 3G, with power and die size metrics on a par with fixed function modem designs. This new era in DSP technology along with strong customer traction for its LTE DSPs ideally positions CEVA to further expand their leadership in DSP IP as we enter a new era of wireless communications.” T

he magic word is “special purpose DSP”, this means that the one size fits all DSP IP concept is no more adapted to the market demand. Gideon Gideon Wertheizer, CEO of CEVA, explains this new paradigm: “For next-generation products requiring even more DSP horsepower – fixed function DSPs or DSP-configured CPUs are unable to match the flexibility, performance, power and die size of our new DSP offerings for baseband (CEVA-XC), audio/voice (CEVA-TeakLite-4) and imaging /vision (CEVA-MM3000).” If we look at these three different families:

- CEVA-TeakLite DSP family is the most successful licensable DSP family in the history of the semiconductor industry, with more than 3 billion chips shipped, over 100 design wins, 30 active ecosystem partners and more than 100 audio and voice codecs and software applications available.

- CEVA-XC family of DSPs is designed specifically to overcome the stringent power consumption, time-to-market and cost constraints associated with developing high-performance multimode baseband solutions. It supports multiple air interfaces for various applications such multimode cellular baseband (2G/3G/4G), connectivity (WiFi 802.11ac, GNSS), digital broadcast (DVB-T2, DVB-S2, ATSC) and smart grid.

- For imaging and vision applications, the CEVA-MM3101 is a unique, fully programmable platform that is dedicated to addressing the extreme computational needs of any image enhancement or vision use case. By off-loading the device’s main CPU and replacing multiple hardwired accelerators for performance-intensive imaging and vision processing tasks, the highly-efficient CEVA-MM3101 dramatically reduces the power consumption of the overall system, while providing complete flexibility in terms of standards, imaging functions, and vision applications.

To learn more about CEVA DSP and platforms, visit http://www.ceva-dsp.com/DSP-Cores.html.

What is the electronic application exhibiting the highest growth and generating huge profits for (two) successful OEM (Apple and Samsung) in 2012? What is the wireless communication standard that any smartphone manufacturer has to support, if he wants to be successful tomorrow? Long Term Evolution, or LTE! The LTE baseband shipments have been forecasted by Strategy Analytics (note that they forecast IC shipments, not end devices and generally the chips are shipped one quarter before the device is sold in the market). We have used the data extracted from the Table (below) to build a graphical view of the smartphone (red) and LTE chips (blue) forecast (see the above picture). Also, note that baseband numbers include shipments to non-handset devices such as the Apple iPad 4G and Samsung Galaxy Tab 4G.

Clearly, LTE is the place to be today to prepare the future shipments, as these will bring revenue under the form of royalties.

- CEVA has now achieved more than 20 customer design wins for its LTE/LTE-Advanced DSP technologies, reaffirming the company’s dominant position as the #1 DSP licensor for wireless baseband. CEVA’s publicly announced customer wins for LTE/LTE-Advanced include Broadcom, Intel, Mindspeed and Samsung, in addition to a number of unannounced tier 1 handset and infrastructure OEMs.

- According to Stuart Robinson, Director of the Strategy Analytics Handset Component Technologies service, “Based on our analysis, LTE basebands powered by CEVA DSP cores are now shipping in the millions, second to Qualcomm. These shipments are expected to further accelerate as new CEVA-based LTE smartphones are being rolled out by tier 1 OEMs.”

Finally, recently published industry data by The Linley Group revealed that CEVA continued to dominate the DSP IP shipments market in 2011, with shipments of CEVA-powered DSP chips surpassing that of any other DSP IP licensing company by more than a factor of 3x. We can guess that the cumulated shipments of CEVA DSP-powered chips (not core) will continue to outperform the DSP IP competition in the future…

Eric Esteve from IPNEST –

CDNLive Call For Papers

The Silicon Valley CDNLive, the Cadence user conference, will be on March 12-13th 2013 in Santa Clara. But the heart of CDNLive are customer presentations and the call for papers is now open. The deadline is December 4th (at 5pm PST for people who really like to come down to the wire). At this point only an abstract is required.

There is a huge list of suggested topics, but topics that will be hot in 2013 are:

- Sign-off

- Advanced node

- 3D IC

- Low power

- Mixed-Signal

- Design IP

- System Design and Verification

- PCB Design

If your paper is accepted then you could win an iPad4. You can also attend CDNLive for free. Conference registration will open in January.

More details are here.

2nd International RRAM Workshop at Stanford

The 2nd International Workshop on Resistive RAM. The workshop was the second installment of an annual series organized by Stanford University and the Belgian research institute Imec. Like most RRAM workshops, this year’s event featured talks focusing on the physics of RRAM devices and their underlying switching mechanism(s). However, roughly equal attention was paid to design and architecture aspects of RRAM technology and to potential RRAM applications other than its use as a NAND replacement, such as a talk on low power programmable logic from LEAP/NEC. This seemed to reflect a general feeling that the R&D efforts on RRAM of the past decade may soon yield a usable technology, or perhaps even several technologies from different companies. The workshop also gave particular emphasis to the question of what the requirements are for a selector device for RRAM, and how close various selector technologies are to meeting these requirements. For more info, follow the link ReRAM-Forum.com

The Auto Industry Speaks @ Renesas DevCon

This year’s Renesas DevCon in Orange County, CA kicked off yesterday with an impressive lineup of speakers, record attendance, and an increased focus on automotive.

“TheAuto Industry Speaks,” an Expert Panel organized by Martin Bakerof Renesas, featured:

- Yoichi Yano, RenesasExecutive VP and Member of the Board, who early in his career designed the original 850 MCU, the world’s most popular automotive controller

- Michael Grimes, Technical Fellow, Semi, MCU & Controller Architecture at General Motors

- Ian Wright, CEO at Wrightspeed, former cofounder Tessla Motors

- Bob Adams, Hardware Team Leader, Interior, Body and Security, at Continental

- Mike Bourton, Founder of Grid2Home

Insights? Sustainable mobilityclearly emerged as one of the big challenges, requiring both technical solutions and government/infrastructure/other aspects. Ian commented: Burning oil is a problem; some vehicles burn natural gas; we focus on electric cars, but the problem is still energy! Michael Grimes: It’s the same as always, we need to be more efficient, but we’ve picked all the low hanging fruit, so it becomes more expensive to improve efficiency. Now, MPUs for state-dependent behavior (based on altitude, warm or cold engine, etc.) may help reduce energy consumption. Yano-san: Automotive MPUs used to consume a lot of power, now they consume less; this allows tens of MPUs per car. Bob: Electric vehicles are even more sensitive to electronics power (range problem). New opportunities in controller design to lower power consumption. Ian responded: But, electric cars consume lots of amps, the MPU power is negligible. Bob: We need infrastructure for charging vehicles, complex issues.

Money, money, money:spirited discussion of why $40K for an electrical vehicle (EV) comparable to a $20K auto! In defense: expensive batteries, motors, extra electronics, low tire rolling resistance, etc. Lots of redundancy: electric storage and fuel storage, more cooling systems, engines for electric and fuel. The bad news: “The MPUs cost nothing compared to other components. so Moores Law will not help us….nor will volume. We may get to fewer, larger chips per car, take some silicon costs out, but this is a small part.”

Panelists also discussed the types of vehicles that represent the biggest growth for electric or hybrid propulsion. Ian stated, yes, look for vehicles that use a LOT of fuel, such as heavy duty trucks; especially those with a lot of stop/start action like garbage trucks (3 year payback for them vs passenger cars, which today require 7 yrs or government subsidy for ROI.) Range anxiety is a huge problem for electrical cars. Big batteries increase weight and cost, as well as time to ROI so range-extended EVs are important, because they can use existing infrastructure (gas). Michael G: Range anxiety is very real; why Chevy Volt is successful. Mike B: Other technologies like solar, wind, must be stored, so battery technologies must evolve for many applications.

AUTOSAR:effective in addressing industry challenges? Mike G: Autosar is to automotive software as Windows is to pc software…..(laughter.) The general consensus was that Autosar does not achieve all goals, but achieves many of them: not perfect; definitely committee-developed; and its layered OS can represent significant overhead when in real time and need fast response. But, it’s the predominant architecture, helps manage complexity (100M lines of code per car typical), and is a good first step to unify the industry which is key. Note: many Tier 1 companies say they have taken Autosar and customized it.

Autonomous vehicleswere recently touted, will this be a revolutionary or evolutionary change? 2 years or 10? In fact, depending on how we define autonomous, many capabilities already available in the helped or aided category, like cruise control and backup visibility/ monitoring. Ian said, his cars have driver assistance like slip control and they could go further, but don’t; must use driver control as gospel to avoid liability, especially in the US. Panelists felt the time will come; safety must be considered; needs lots of computing power, but we have this technology. Opportunities: Lots more electronics!!! Much more throughput would need to be added. Wireless and infrastructure. Sensing as well as compute power. Power and heat management for added electronics. Yano-san commented that active safety and autonomous cars are definite roadmap drivers; constant balance needed re: capability and power consumption of chips (sensors and processors.) A very exciting area. Emerging opportunity for vehicle-to-vehicle standard communications… standards important here… this fuels the dream of fully autonomous vehicles.

Have software toolshelped automotive get this far?

A resounding YES and thumbs up to model-based design, design re-use, and tools that support huge projects with many people, distributed around the world.

Toshihide Tsuboi, Senior VP for MCU Business at Renesas,contributed a

perspective: Previously, in the first wave, minimizing fuel consumption, and emissions, were the main drivers for advanced electronics controls in automotive. The current frontier is functional safety, such as ISO26262 standards, and again MCUs must handle these challenges. Next, the exciting emerging area is ADAS, Advanced Driver Assistance Systems, which includes performance of MPUs for information handling, as well as sensors, displays, etc. At this time, no one really knows yet the amount and speed of information that will ultimately be involved in sophisticated ADAS, but it is increasing dramatically.

Takeaway: As Michael Grimes commented, electronics has made all the difference in the last few decades! Complexity up, power down. Great opportunity persists for automotive semiconductor and electronics companies who accurately gauge and respond to the trends…and thanks to Renesas DevConand all panelists for sharing the insights!

(Note: The above is paraphrased from notes, not verbatim, captured gist of remarks.)