It was a year ago that Paul Otellini made his surprise announcement that he was stepping down as CEO of Intel. Soon after, I wrote an article asserting that the only correct choice for his replacement was Nvidia’s CEO Jen Hsun Huang. I went beck to reread what I wroteand I can scarcely say I would change anything I put in the article assuming Intel intends to continue down the path of trying to win mobile with Atom and limiting the Foundry prospects to non-compete fabless players like Cisco and Altera. Andy Bryant’s confession of missing the tablet market aside, the company though moves closer to a split due to financial gravity that is trying to shake Intel’s Board and Executives to the reality that the Fabs are more valuable than mobile Atom where x86 is valued at next to nil.

Intel is evolving into two companies and now the Fab side of the house represented by Andy Bryant and newly minted CEO Brian Krzanich have the reigns. They know that the company is still well funded with the awesome Data Center Group and traditional x86 PC client group that has been able to execute a slow retreat by aggressively moving into the higher ASP ultrabook market, where AMD and nVidia do not play well for cost, space and power reasons. Intel charges a premium with its ULV processors, but this may not last over the long run as mobile processors are undercutting the premium by as much as several hundred dollars. The other side is the Foundry that demands $11B of capex each year to keep them running with bigger bills on the 450mm horizon. Mobile atom is the worst of times in the famous Dickens novel. It is on track to lose $2.4B on $4B in sales this year.

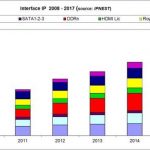

At first the analyst cheered at the news that Intel would quadruple tablet processor sales in 2014 to 40MU. Then the cheers changed in tune to what one might hear in the Bronx when the home team fails as CFO Stacey Smith announced revenue would be flat in 2014. Digging deeper, one sees that to sell 40M processors requires quite a bit of marketing dollars. Intel doesn’t discount processors, they instead offer an ad campaign to get the word out that Intel Inside is now alive inside mobiles. Analysts are not thrilled when there is no light at the end of the tunnel to Intel’s mobile adventures.

If Intel were to split, I would still place my money on Jen Hsun Huang as the true Andy Grove heir that could make sense of what to build from servers to mobiles with the optimum mix of processor, graphics and communications. Selecting Jen Hsun would create a monopoly in the data center and close off all competitors to a piece of business that may be larger than the PC x86 group in 5 years time. Alas, it will probably not come to fruition, unless Intel enters more dire straits and the board is replaced with folks who want not just change but strong growth.

It is not hard for someone of Jen Hsun’s experience to see that tablet has split irreconcilably and that the corporate windows piece can and should be supported by a trimmed down version of Intel’s Broadwell processor while consumer is tailing away with ARM as the best low cost solution. With a sea of solutions, branding and simplicity still count as valuable to buyers who care, both corporate and consumer. Everyone looks for a company to trust.

The irony of Intel’s dilemma is that for many years they espoused the beauty of the PC’s horizontal market with each slice providing unique value. If you doubt, go read Andy Grove’s “Only the Paranoid Survive.” Paul Otellini, in his final two years would exclaim to Wall St, that Intel liked to get paid twice for its intellectual property, the first for the foundry and the second for the x86 architecture. It appears this is not so in the mobile space and truly it is not x86 that determines the second stack value but all that legacy software that needs to run as is.

Today Mr. Market clearly is saying that the Foundry must take its independent horizontal slice and create value separate from Xeon and Core x86 processors. The high castle walls that protect Xeon and Core are not transferrable to mobile, where ARM started out with an enormous lead and where Apple has virtually declared that custom processors will be forever closely coupled to iOS. Why not build for them and fill a fab or two at the expense of rapidly gaining rivals Samsung and TSMC.

Waiting for Intel to split the company is not what most investors envisioned and it may turn into a long drawn out game until someone like a Carl Icahn comes in and forces the hands of the board. Who will be CEO at the split is anyone’s guess but to at one moment in the Analyst Meeting proclaim that the Foundry is open to all and the next minute discuss how great mobile Atom is going to be for Intel’s future is to essentially mean that the great trigate process is beholden to the smallest part of the business that may start bleeding not a trickle but a flood if 40MU are sent to wayward homes.

lang: en_US