Back in the early days of ASIC when we had just two and then (wow!) three layers of metal, place and route was done by putting the standard cells in rows with gaps between them and then using a specialized router to do the interconnection. It would use one layer of metal horizontally and one vertically and avoid jogs. This was called a channel router. For digital place and route today we have lots more layers of metal and we are not restricted to keeping our routing contained in the channel.

But memories are different. They have fewer layers of metal and end up with long narrow areas between the memory arrays and around the outside. Memories are also early into new processes and the first that have to deal with more restricted design rules. As a result, there is a need for routing this sort of area with long jogless nets, just like in the old days of 3-layer metal ASICs.

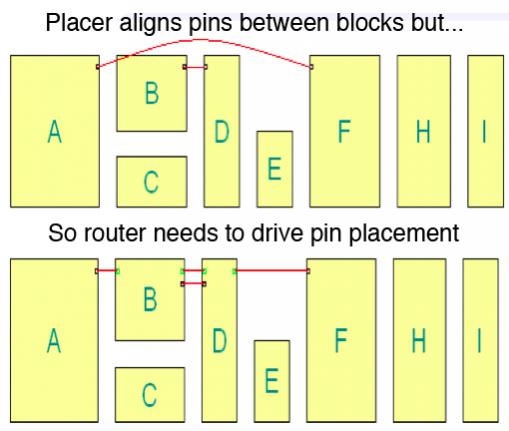

Normal digital place and route, or a shape-based router, does not give the right results, producing too many jogs, too many vias and is not controllable enough by the designer. But a straightforward implementation of a 1980s channel router isn’t adequate either. The connection points are inside the blocks, care needs to be taken feeding signals through the blocks. What is required is a smart way to create the pins that is aware of just how the channel router is going to behave. Otherwise it is too easy to create designs where one pin blocks another route (remember, we are avoiding jogs and vias). The router needs to drive the pin placement.

Pulsic’s spine and stitch router does this. The pin placement is driven by the router so that eventually everything can be routed with long straight wires. There is an example below, although, of course, a real example would likely involve thousands of nets. The spine router with pin placement can do in 30 minutes what used to take a designer doing it manually 3 weeks. Using intelligent pin sorting the router will typically complete over 95% of the nets leaving just a handful where the designer needs to guide the tradeoffs involved.