It was an interesting week in Taiwan for sure. Typhoon Fanapi, lightning storms, the first 28nm production silicon, foundry re-orgs, and most importantly Moon Cake pastries! Wednesday was the Chinese Moon (Zhongqiu)Festival, in Taiwan it is a National holiday commonly celebrated by people barbecuing various meats outdoors. I just love those moon cakes!

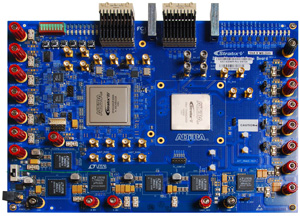

The biggest news is that Altera demonstrated production silicon @ TSMC 28nm for the Stratix V FPGA family, originally unveiled in April of this year. Altera is using the HP (high performance) version of TSMC 28nm, the same process that the GPU vendors use, so expect TSMC 28nm production silicon announcements from Nvidia and AMD/ATI in the next quarter or so. Altera was the first to yield on TSMC 40nm so they clearly know what they are doing. Xilinx will also use TSMC 28nm, expect an announcement this week.

Speaking of Nvidia, CEO Jen-Hsun Huang did a candid interview on the technical difficulties of the TSMC 40nm Fermi chip:

“The parasitic characterization from our foundries and the tools and reality are simply not related, at all. We found a major breakdown between the models, the tools, and reality.”

You can interpret this different ways and the press certainly will. Enlightened semiconductor people know however that process models evolve while processes ramp. Early access companies such as Nvidia, Altera, AMD/ATI, Qualcomm, etc… start designs with pre production process models. The amount of changes to the models varies but 40nm broke revision records for sure. I have seen this many times while working with early access IP companies.

As I blogged in:

- Moore’s Law and 40nm Yield

- TSMC 40nm Yield Explained

- EDA Marketing Fail TSMC Process Variation

Process variation really kicked in at 40nm and those that prepared yielded, those that didn’t, didn’t, simple as that. The process models had variation built into them but the main stream EDA tools did not. So Jen-Hsun was right, there was a major breakdown between the models and the tools. The reality breakdown however was a design management issue within Nvidia, which Jen-Hsun acknowledged in the interview.

The other news from Taiwan is the departures of Fu-Cheih Hsu and S.T. Juang from the TSMC Design and Technology Platform unit, founders of the TSMC Open Innovation Platform (OIP). EETimes broke the story on 9/20/2010 with “TSMC’s Design Guru Resigns”. Fu-Cheih actually left in August (typical mainstream media lag) with S.T. Juang following him in September.

I’ve received a lot of emails on this from vendors and customers alike. The big question is: will the TSMC OIP initiative continue? The answer of course is: YES it will. Fu-Cheih’s replacement is Cliff Hou who is even more qualified to advance the OIP agenda. Cliff is much more approachable, easy to work with, and has more “hands-on” semiconductor design enablement experience.

Cliff joined TSMC in Dec 1997 as a section manager responsible for process design kit (PDK) and reference flow development from 0.35m to 65nm. In 2007 Cliff became senior director of TSMC in-house IP development. TSMC IP includes: standard cells, IO’s, embedded memory compilers, analog blocks, and high-speed interface modules. He has a B.S. degree from National Chiao-Tung University, and a Ph.D. from Syracuse University, New York. He is also a member of the board of directors of Global Unichip Corp. Cliff knows semiconductor design enablement, absolutely.

Share this post via: