The Mentor Graphics test folks and ASSET Intertech have teamed up to provide a series of free DFT seminars in the US, Europe, and Asia. The first one is in Austin, TX on February 19, 2015, and the last is in Tokyo on April 24. Hereis the full list of locations and dates.

The morning session covers IJTAG. The new IEEE 1687 Internal JTAG (IJTAG) standard is changing the way the industry validates, tests and debugs chips and circuit boards. IJTAG-based methods are more cost-effective, more accurate, faster and less time-consuming for you. IJTAG’s software-driven tests and validation routines are initiated from instruments embedded inside chips providing key benefits from a silicon or board perspective based on the type of problems you are trying to solve. This seminar will highlight the synergy between Mentor and ASSET tools and how the IJTAG ecosystem that they provide will accelerate adoption of this technology. Don’t miss the chance to learn how to tap into this useful IP.

The morning session covers IJTAG. The new IEEE 1687 Internal JTAG (IJTAG) standard is changing the way the industry validates, tests and debugs chips and circuit boards. IJTAG-based methods are more cost-effective, more accurate, faster and less time-consuming for you. IJTAG’s software-driven tests and validation routines are initiated from instruments embedded inside chips providing key benefits from a silicon or board perspective based on the type of problems you are trying to solve. This seminar will highlight the synergy between Mentor and ASSET tools and how the IJTAG ecosystem that they provide will accelerate adoption of this technology. Don’t miss the chance to learn how to tap into this useful IP.

Related — IJTAG was recently ratified by the IEEE-SA standards board. Its a bouncing baby IEEE standard!

Who should go?

- DFx Engineers who need to insert the IJTAG networks and gain the benefits of accessing IP within the silicon.

- Board Designers who want to gain the benefit of enhanced board validation and test features accessed by IJTAG.

- Test Managers who want to improve their overall test process and resolve test challenges that cannot be addressed with current test technologies.

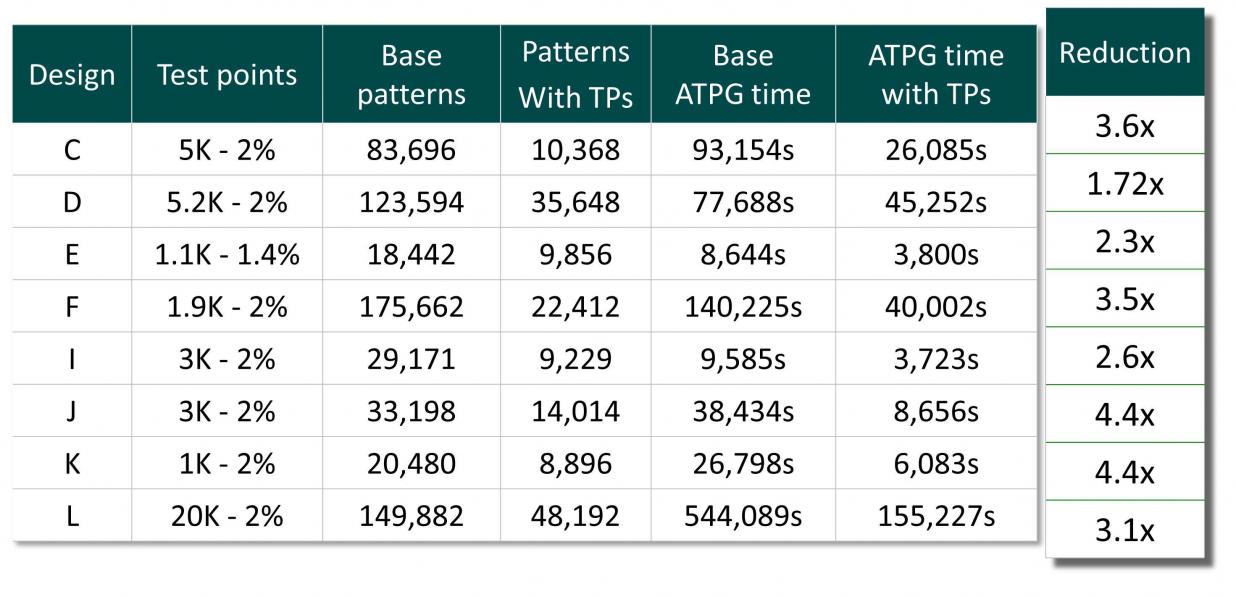

Following a delicious lunch, the afternoon seminar is all about the next big thing in test compression—EDT Test Points. Embedded test compression was commercially introduced over a decade ago and has scaled to well beyond the 100X range envisioned when it was first introduced. However, growing gate counts enabled by new technology nodes as well as new fault models targeting defects within standard cells are driving the need for even greater compression levels. This session will begin with a review of leading-edge test compression features and techniques and will then introduce and focus on an exciting new technology, called EDT Test Points, which has been developed specifically to work with embedded compression to further reduce pattern volume for compressed patterns. Numerous customer beta engagements have shown that EDT Test Points can reduce compressed pattern counts on an average by a multiplicative factor of 2-4X, without affecting test coverage, and even for designs with the most aggressive embedded compression configurations.

Related — Daniel Payne recently wrote a very good article on EDT Test Points, More Test Points are Better

Who Should Attend?

- Designers, DFT engineers, and test consultants involved with creating testable ICs and producing the manufacturing test sets

- Product engineers responsible for manufacturing test of ICs

- Test managers looking to minimize manufacturing test costs while maintaining or improving test quality

Registernow for an ASSET InterTech and Mentor Graphics DFT Technology Seminar near you!

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.