Gim Tan at Magma did a webinar on analog circuit optimization, so I watched it today to see what I could learn about their approach. Gim is a Staff AE, so not much marketing fluff to wade through in this webinar.

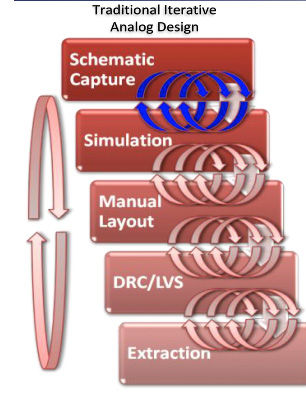

The old way of designing custom analog circuits involves many tedious and error prone iterations between front-end (Schematic Capture, circuit simulation) and back-end (layout, DRC/LVS, extraction):

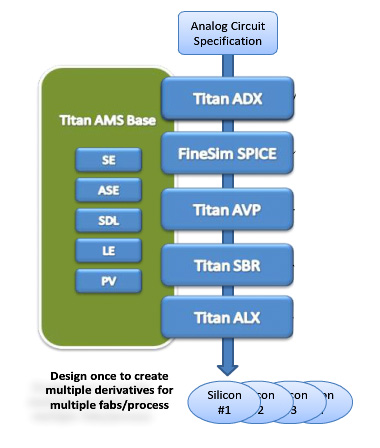

The Maga-based custom IC design flow uses:

- Model-based cells called FlexCells in Titan ADX:

- Circuit simulator, FineSim SPICE

- Floorplan, Titan AVP

- Automated routing, Titan SBR

- Automated IC layout migration, Titan ALX

Titan AMS has the following tools:

- Schematic Capture

- Analog Simulation Environment (wafeforms, cross-probing)

- Schematic Driven Layout (SDL), uses iPDK or pCells or IPL

- Layout Editor

- Process Verification (violation analysis in a GUI)

Foundry support for Titan AMS:

- TSMC: 180nm, 65nm, 40nm, 28nm. AMS Reference flow 2.0

- TowerJaxx: 180nm, AMS Reference flow

- LFoundry: 150nm

Titan Analog Design Accelerator (ADX)

- Optimize, re-size schematics

- Process porting

- Feasibility studies

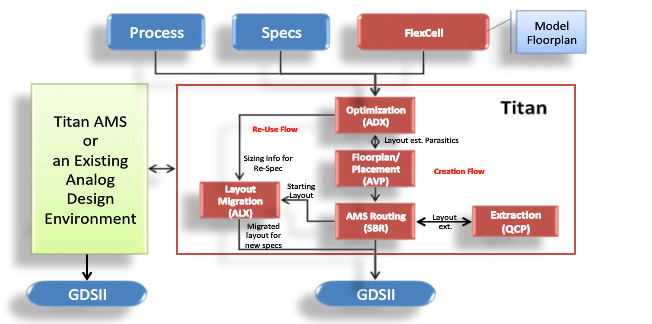

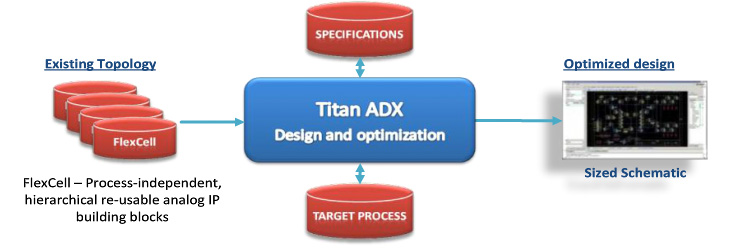

The design flow with Titan ADX is:

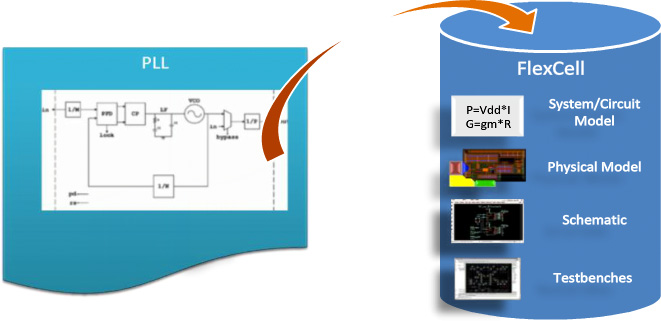

With this flow you can start by importing your old schematics and transistor-level netlists. What’s unique about this flow is the use of FlexCell, which adds a mathematical view using Matlab equations for a circuit along with the traditional views: Schematic, Layout, Testbench

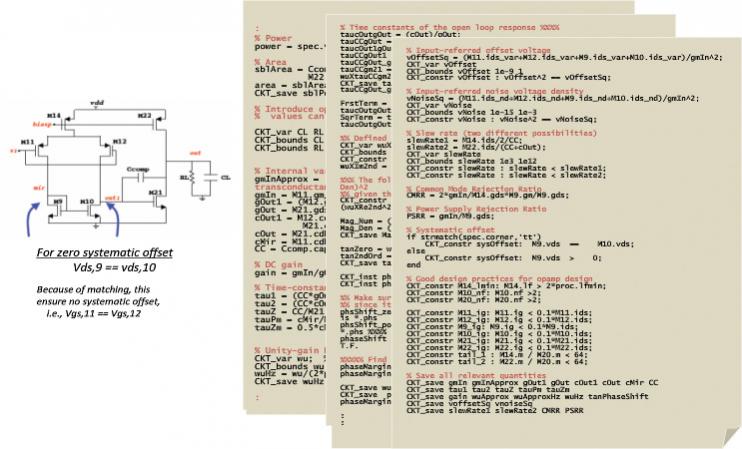

There are ready-made FlexCells for you to start using right away and to help learn model behavior, intent and set constraints. Here’s an example two-stage PMOS Op-Amp FlexCell:

A predecessor to Titan ADX was a technology from Barcelona Design where they used a proprietary modeling language called Flamingo. The learning curve for Matlab should be much shorter than for the old Flamingo code.

Once you’ve defined your analog design as a FlexCell then you can do analog IP optimization with Titan ADX:

Titan ADX is model-based optimization, not simulation based, so that makes it quite unique in the EDA industry. Synopsys also has a simulation-based optimizer (acquired Analog Design Automation), so it will be interesting to see the new product roadmap and if Titan ADX is carried forward.

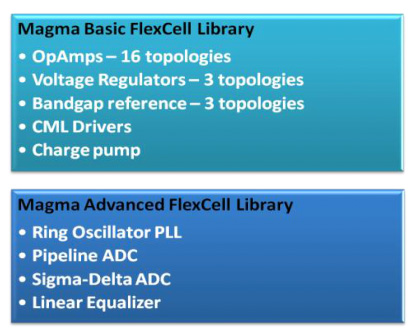

Magma has a library of FlexCells that you can use:

TSMC is using FlexCells to retarget their own IP for customers as needed. Fraunhoffer is also offering FlexCells.

Titan ADX flow:

[LIST=1]

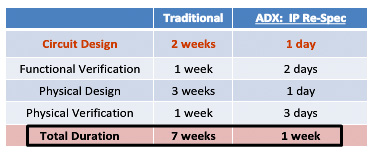

PLL Migration

A traditional migration to a different 65nm process node takes 7 weeks (circuit design, functional verification, physical design, physical verification), while with ADX the same task is doe in 1 week or a 7X improvement in time. This kind of improvement assumes that you have all the required FlexCells in place before hand. If you had to write and verify new FlexCell models then that would decrease the time improvement.

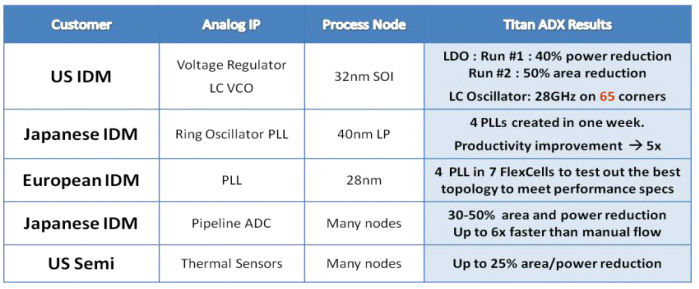

Real Customers

So far this model-based optimization approach sounds unique and powerful, however who is really using it? Panasonic and TSMC plus the following are using it:

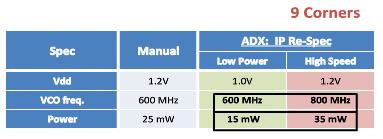

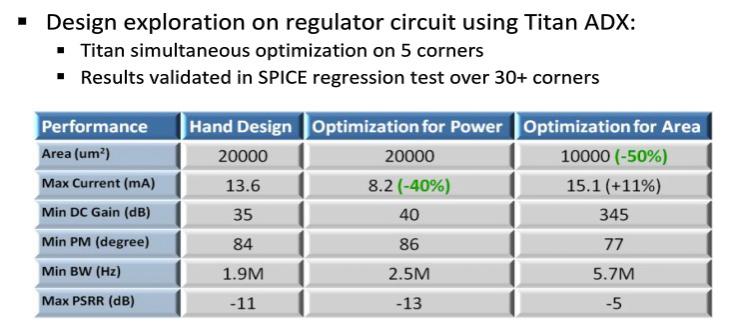

One Model, Multiple Results

Using FlexCells and Titan ADX you can optimize for either power or area, or something in between:

Summary

Magma offers model-based optimization in Titan ADX which is a different approach than simulation-based optimization. This model-based approach is certainly more elegant than the brute force simulation-based optimization approach, and you’ll have to decide if you can just quickly use the existing FlexCells off the shelf or have to invest in writing your own MATLAB equations for new FlexCells.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era