You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

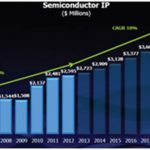

SemiWiki blogger Eric Esteve does an excellent job writing about all of the semiconductor IP available, and the popularity of IP is only growing more each year. Here’s a projection from IBS about semiconductor IP showing revenues of $4.7B by 2020:

Analyst Gary Smith divides IP into three broad categories: Functional, Foundation… Read More

Software engineers and firmware designers can find bugs, update their code and re-distribute to the users. In the consumer electronics world this means that my smart phone apps get updated, and my Android OS gets updated on a somewhat regular basis, however on the hardware side the design and verification of an SoC must be close … Read More

Earlier this month I blogged about Power Management Policies for Android Devices, so this blog is part two in the series and delves into the details of using ESL-level tools for simulation and analysis. The motivation behind all of this is to optimize a power management system during the early design phase, instead of waiting until… Read More

My Samsung Galaxy Note 2 phone lasts about 1.5 days on a single battery charge, thanks in part to the clever power conservation approaches like when the screen is automatically dimmed then turned off after no activity. Mobile phones and many other battery-powered devices used today all need power-saving designs, which then means… Read More

I’ll never forget debugging my first DRAM chip at Intel, peering into a microscope and watching the aluminum interconnect actually bubble and dissolve as the voltage was increased, revealing the destructive effects of Electromigration (EM) failure. That was back in 1980 using 6 um, single level metal technology, so imagine… Read More

Just as important as block RAMs, IO and DSP48’s is what interconnect or fabric is going to be used when considering SoC FPGA designs. I think Xilinx has found the winning combination. What is paramount to the new SoC FPGA methodologies is not only the challenge of moving huge amounts of data around; we are now to consider data… Read More

IC designers of passive devices often use empirical approaches to perform High Frequency Analysis (HFA), however there is at least one new approach being offered by Mentor Graphics using a tool flow of:

…

Read More