In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Tag: white paper

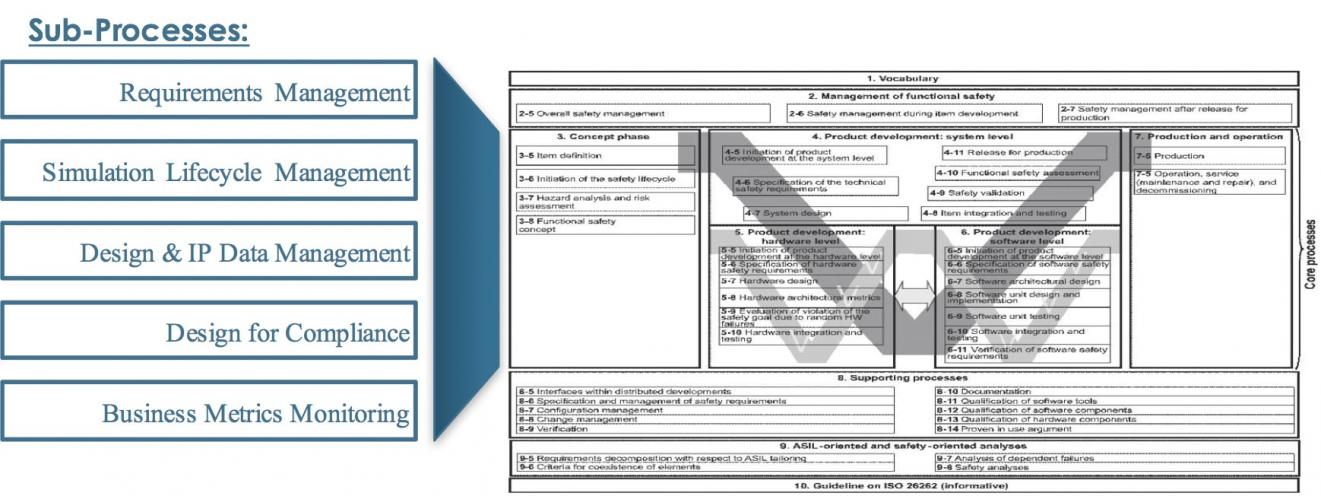

ISO 26262 Traceability Requirements for Automotive Electronics Design

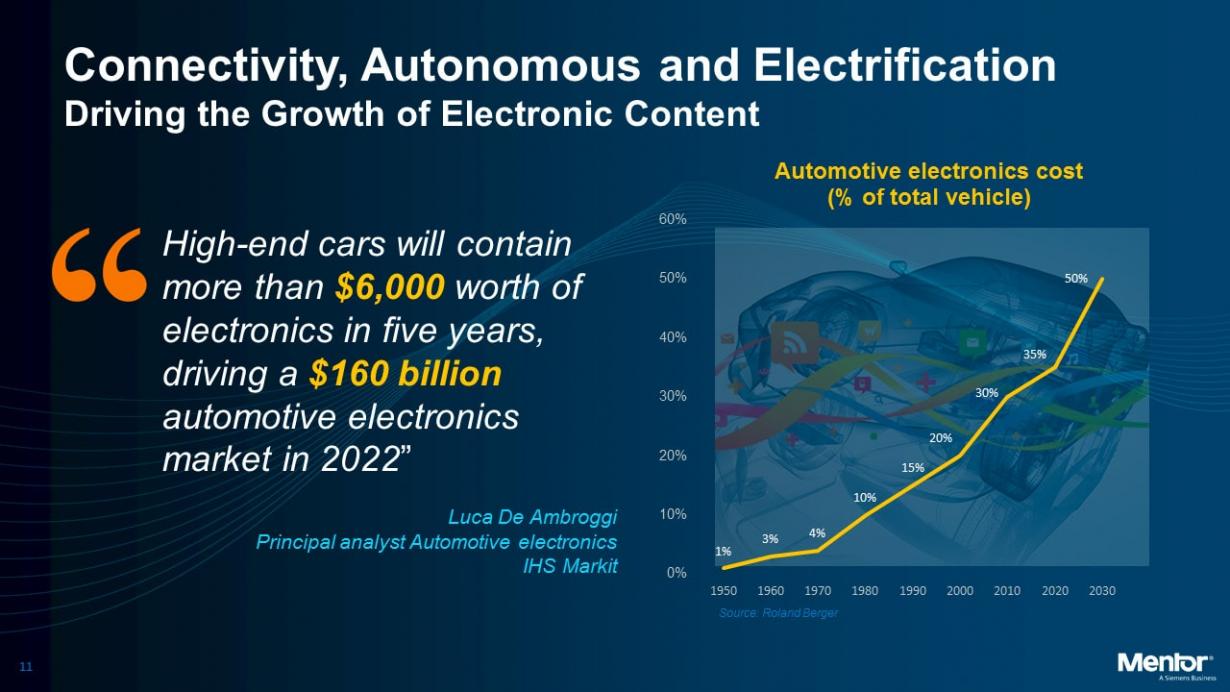

Reading the many articles on SemiWiki and other publications we find experts talking about the automotive market, mostly because it’s in growth mode, has large volumes and vehicles consume more semiconductors every year. OK, that’s on the plus side, but what about functional safety for automotive electronics?… Read More

Mentor’s Approach to Automotive Electrical Design

Most of us continue to drive cars and for me there’s always been a fascination with all things electrical that go into the actual design of a car. I’ve done typical maintenance tasks on my cars over the years like changing the battery, installing a new radio, replacing bulbs, changing a fuse, swapping out dashboard lights,… Read More

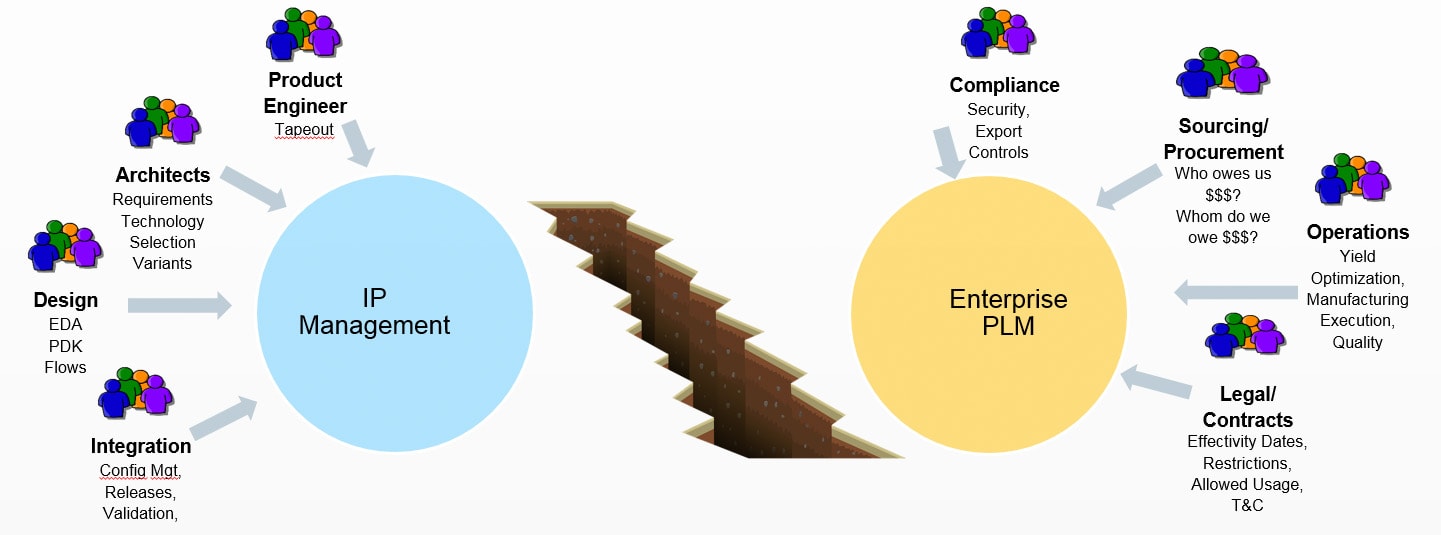

Combining IP and Product Lifecycle Tools

No single EDA company provides all of the tools needed to define requirements, design exploration, track IP, simulate, manage and verify a complex SoC system, so it makes sense that EDA vendors and point tool companies have tools that work together to achieve all of these difficult tasks. Systems design has been around for decades… Read More

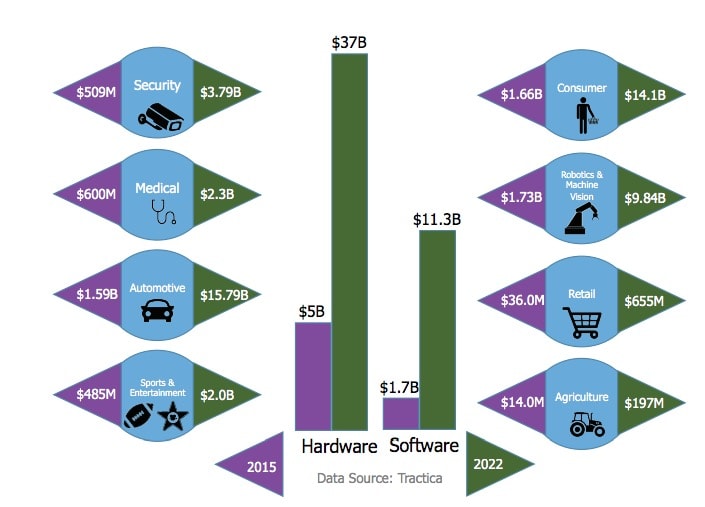

Computer Vision and High-Level Synthesis

Computer vision as a research topic has been around since the 1960’s and we are enjoying the benefits of this work in modern-day products all around us as robots with computer vision are performing an increasing number of tasks, even our farmers are using computer vision systems to become more productive:

- AgEagle® has a drone

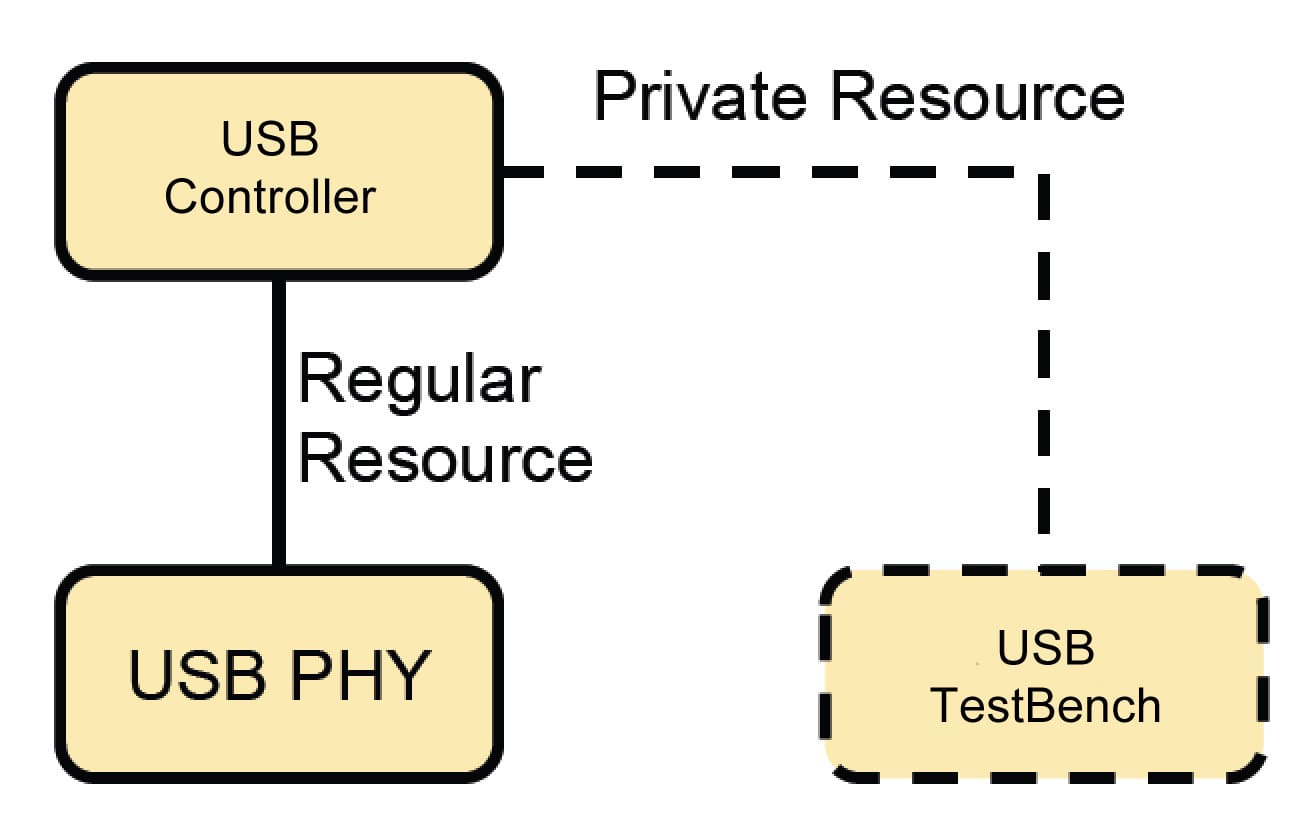

Hierarchy Applied to Semiconductor IP Reuse

When I first started doing IC design back in 1978 we had hierarchical designs, and that was doing a relatively simple 16Kb DRAM chip with only 32,000 transistors using 6um (aka 6,000 nm) design rules. SoC designs today make massive use of hierarchy at all levels of IC design: IC Layout, transistor netlist, gate level netlist, RTL … Read More

Time is Money, Especially when Testing ICs

Semiconductor companies are looking for ways to keep their business profitable by managing expenses on both the design and test side of electronic products, which is quite the challenge as the trends show increases in test pattern count and therefore test costs. Scan compression is a well-known technique first created over 15… Read More

Dassault Systemes Hosts New Microsite Focused on IP Reuse Challenges

I recently wrote an article about networks-on-chip (NoC) and how Systems-On-Chip integrated circuits (SoCs) are becoming increasingly more complex and heterogeneous in nature. While researching for that article I came upon a new micro-site by Dassault Systemes that goes into great detail about the operational challenges… Read More

Requirements Management and IP Management Working Together

I first heard about requirements management back in 1995 while marketing a graphic HDL entry tool for an EDA vendor, and it sounded like a very useful automation approach, however our team quickly discovered that there were too many different vendors for requirements management, so there could be no simple way to integrate with… Read More

More Test Points are Better

I got really involved in testability back at CrossCheck in the 1990’s when they designed a way for Gate Arrays to have 100% observability without any Design For Test (DFT) requirements on designers. The Japanese Gate Array companies loved this approach and their customers enjoyed the highest test coverage without being… Read More