You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

New concepts and breakthroughs in VLSI processes and devices including Memory, Logic, I/O, and I/F (RF/Analog/MS, Imager, MEMS, etc.) – Advanced gate stack and interconnect in VLSI processes and devices – Advanced lithography and fine patternig technologies for high density VLSI – New functional devices… Read More

We live in an age of abundant information. There is a tremendous exchange of ideas crisscrossing the world enabling new innovative type of products to pop up daily. Therefore, in this era there is a greater need to understand competitive intelligence. Corporate companies today are interested in what other competitors are brewing… Read More

Daniel Nenni was gracious enough to encourage me to conduct a brief webinar describing a new reference text, recently published by Prentice-Hall, part of the Semiwiki Webinar Series.

VLSI DESIGN Methodology Development Webiner Replay

Background

I was motivated to write the text to provide college students with a broad background… Read More

Me.

In the early stories of this series (Weeks three though six), I talked about what I believe were the three seminal events in the history of the semiconductor: Shockley’s invention of the transistor, Noyce’s invention of the integrated circuit, and Intel’s 1971 — the introductions of the first commercially successful… Read More

The year is now 1991 and in search for a more peaceful life we decided to move to Canada. At that time, very few companies had advanced flows in VLSI but Ottawa having BNR, Northern Telecom, Mitel, etc., looked to be the most promising place. After a few hiccups in finding a job, I landed in MOSAID, a small company with35 people at that … Read More

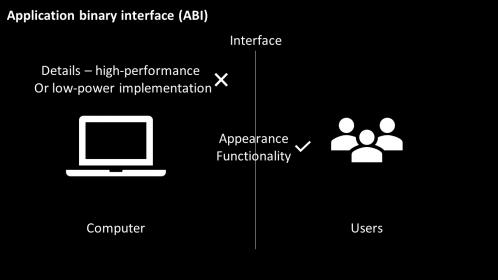

Starting a career in static timing analysis domain, and now actively working on an opensource implementation flow of RISC-V architecture, has been a journey. For last couple of months, I guess from around March this year, I was hooked to RISC-V buzz which was all over my Linkedin, my messages.

Being an STA and Physical design engineer,… Read More

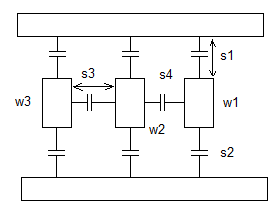

Layout parasitic extraction (LPE) has three primary goals – accuracy, capacity, and throughput. Traditionally, LPE tools have offered two methods for capacitance derivation, with tradeoffs on these goals:… Read More

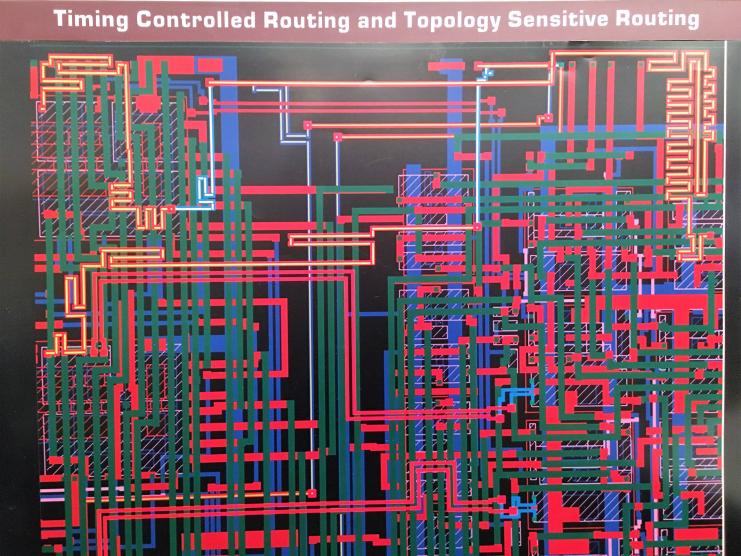

As I travel a lot in the last 15 years and visited customers as well as friends I was many times invited to talk to the Layout teams. The main purpose is always to encourage automation. So I developed a presentation related to market trend, technology trends, and latest tools advancements. In many cases I present updates from DAC (Design… Read More

According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More

Perhaps the most pertinent comment raised by an analyst at Intel’s Investor Forum last week came from Dan Hutcheson of VLSI Research to Brian Krzanich, the COO and head of global manufacturing and supply chain. He said: “I think you sold yourself short on Trigate, the benefit of fully depleted vs. planar and the impact on leakage.”… Read More