I stopped by the AMIQ EDA booth at DAC to get an update from Tom Anderson about their Integrated Development Environment (IDE), aimed at helping design and verification engineers save time. In my early IC design days we used either vi or emacs and were happy with having a somewhat smart text editor. With an IDE you get a whole new way … Read More

Tag: verilog-ams

A Hardware IDE for VS Code Fans

A few times a year, I check in with AMIQ EDA co-founder Cristian Amitroaie to see what’s new with their company and the integrated development environment (IDE) market for hardware design and verification. Usually he suggests a topic for us to discuss, but this time I specifically wanted to learn more about the version of their Design… Read More

CEO Interview: Cristian Amitroaie of AMIQ EDA

AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More

Verilog-AMS connects T-SPICE and Riviera-PRO

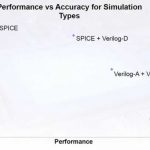

With advances in available IP, mixed signal design has become much easier. Mixed signal verification on the other hand is becoming more complicated. More complexity means more simulation, and in the analog domain, SPICE-based techniques grinding away on transistor models take a lot of precious time. Event-driven methods like… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

Active Power Management in UPF Using SPICE, VHDL-AMS or Verilog-AMS

My former co-worker, Kenneth Bakalar at Mentor Graphics is an expert in AMS modeling languages and UPFmethodology, so he recently teamed up with Eric Jeandeau to author an interesting white paper: Interpreting UPF for a Mixed-Signal Design Under Test. This white paper is based on a presentation made at DVCon earlier this year.… Read More

Accelera Technical Excellence Award

The Accellera Systems Initiative, most well-known for driving the standardization of various aspects of Verilog and SystemVerilog before handing the standards off to the IEEE, has announced that nominations are open for the 2013 Technical Excellence Award. This recognizes outstanding contributions in the creation of EDA… Read More

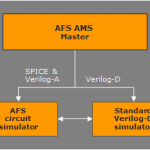

Analog FastSPICE AMS — Simple, Fast, nm-Accurate Mixed-Signal Verification

Verification and AMS are top search terms on SemiWiki so clearly designers have a pressing need for fast and accurate verification of today’s mixed-signal SoCs that include massive digital blocks and precision analog/RF circuits. They need simulation performance to verify the mixed-signal functionality, and they need nanometer… Read More