At a lovely, but chilly, 3DIncites awards breakfast during SEMICON West, I saw Mentor Graphics win in two of five categories (Calibre 3DSTACK was the other winner). Afterwards, I talked to Steve Pateras, the product marketing director of Mentor’s test solutions about Tessent Memory BIST, which was one of the winners. I asked Pateras… Read More

Tag: tsv

Moore, or More Than Moore?

Yesterday was the 2013 GSA Silicon Summit, which was largely focused on contrasting what advances in delivering systems will depend on marching down the ladder of process nodes, and which will depend on innovations in packaging technology. So essentially contrasting Moore’s Law with what has come to be known as More Than… Read More

3D IC: Are We There Yet?

For the last few years, thru silicon via (TSV) based ICs have been looming in the mist of the future. Just how far ahead are they? Xiliinx famously has a high-end gate-array in production on a 2.5D interposer, Micron has a memory cube, TSMC has done various things in 3D that it calls CoWoS (chip on wafer on substrate), Qualcomm have been… Read More

Modeling TSV, IBIS-AMI and SERDES with HSPICE

The HSPICE circuit simulator has been around for decades and is widely used by IC designers worldwide, so I watched the HSPICE SIG by video today and summarize what happened. Engineers from Micron, Altera and AMD presented on how they are using HSPICE to model TSVs, IBiS-AMI models and SERDES, respectively.… Read More

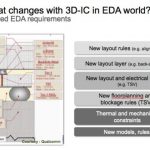

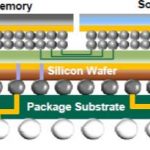

Cadence 3D Methodology

A couple of weeks ago was the 3D Architectures for Semiconductor Integration and Packagingconference in Redwood City. Cadence presented the changes that they have been making to their tool flow to enabled 2.5D (interposer-based) and true 3D TSV-based designs. You know what TSV stands for by now right? Through-silicon-via, … Read More

3D Architectures for Semiconductor Integration and Packaging

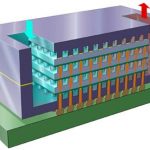

There is obviously a lot going on in 3D IC these days. And I don’t mean at the micro level of FinFETs which is also a way of going vertical. I mean through-silicon-via (TSV) based approaches for either stacking die or putting them on an interposer. Increasingly the question is no longer if this technology will be viable (there… Read More

Dimensions of Electronic Design Seminars

ANSYS and Apache are putting on a new series of seminars about designing future electronic systems. These are only getting more complex, of course, cramming more and more functionality into smaller portable devices with good battery life (and not getting too hot), integrating multiple antennas into a single platform, and TSV-based… Read More

3D Memories

At DesignCon earlier this year, Tim Hollis of Micron gave an interesting presentation on 3D memories. For sure the first applications of true 3D chips are going to be stacks of memory die and memory on logic. The gains from high bandwidth access to the memory and the physically closer distance from memory to processor are huge.

Micron… Read More

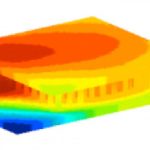

3D Thermal Analysis

Matt Elmore of ANSYS/Apache has an interesting blog posting about thermal analysis in 3D integrated circuits. With both technical and economic challenges at process nodes as we push below 28nm, increasingly product groups are looking towards through-silicon-via (TSV) based approaches as a way of keeping Moore’s law… Read More

Cadence at Semicon West Next Week: 2.5D and 3D

Next week it is Semicon West in the Moscone Center from Tuesday to Thursday, July 10-12th. Cadence will be on a panel session during a session entitled The 2.5D and 3D packaging landscape for 2015 and beyond. This starts with 3 short keynotes:

- 1.10pm to 1.25pm: Dr John Xie of Altera on Interposer integration through chip on wafer on