Seeking Alpha just published an article about Intel and Samsung passing TSMC for process leadership. The Intel part seems to be a theme with them, they have talked in the past about how Intel does bigger density improvements with each generation than the foundries but forget that the foundries are doing 5 nodes in the time it takes… Read More

Tag: tsmc

Webinar: 5 Reasons Why Others are Adopting Hybrid Cloud and EDA Should Too!

With the complexity of transistors at an all time high and growing foundry rule decks, fabless companies consistently find themselves in a game of catch up. Semiconductor designs require additional compute resources to maintain speed and quality of development. But deploying new infrastructures at this current speed is a tall… Read More

China Semiconductor Bond Bust!

– Tsinghua $198M Bond Bust

– Good for memory: Samsung Micron LG Toshiba –

– Not good for chip equipment

– Could China Credit Crunch hit more than foundry embargo?

– Damage to China memory positive for other memory makers

– Not good for chip equip if customers can’t get money

China’s… Read More

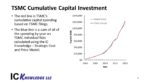

Can Samsung Foundry Really Compete with TSMC?

The semiconductor foundry business has been front page news of late and for good reason, it’s an exciting time in the semiconductor industry and the foundries are where it all begins. Unfortunately, most of the “exciting” news has been overblown but this topic is of great interest, to me at least. Having been intimately involved… Read More

TSMC to Build first US Fab in Arizona!

Well, it’s official, the TSMC Board of Directors approved an investment to establish a wholly-owned subsidiary in Arizona with a paid-in capital of $3.5 billion. As history shows the investment may be more than that but $3.5B is a great starting point. This is being discussed in the SemiWiki Forum and I have been gathering inside… Read More

Leading Edge Foundry Wafer Prices

I have seen several articles recently discussing foundry wafer selling prices for leading edge wafers, these articles all quote estimates from a paper by the Center for Security and Emerging Technology (CSET). The paper is available here.

My company IC Knowledge LLC is the world leader in cost and price modeling of semiconductors… Read More

Are TSMC and Intel Partnering in Arizona?

After months of back and forth TSMC finally announced plans to build a fab in Arizona. The announcement was not made in the press or on the most recent investor call but on LinkedIn. A sign of the times I guess but since they need to hire a bunch of semiconductor people it was more than appropriate.

“We’re delighted to catch up with you … Read More

Downplaying SMIC – Uplaying TSMC

- KLAC sports solid QTR & Guide- Foundry & Logic drivers

- Management remains dismissive of SMIC embargo

- Execution & financials are solid but macro headwinds remain

- Nice September Quarter

KLA reported revenue of $1.54B and Non GAAP EPS of $3.03 versus street expectations of $1.49B and EPS of $2.77. Guidance is for revenues… Read More

Coronavirus Remains Good for Semiconductors but not China

- LCRX puts up a solid QTR and slightly soft guidance

- China Concerns weigh on future but COVID remains driver

- Memory spend could be better & help offset China

Solid September Quarter

Lam reported Non GAAP EPS of $5.67 versus $5.19 street and Revenues of $3.18B which was $70M better than street expectations. Lam obviously does … Read More

Intel TSMC Update!

Based on the Intel investor call yesterday here are some interesting comments Bob Swan made related to Intel outsourcing manufacturing and 7nm progress. Let’s start with the prepared statement:

Bob Swan: “Over the last couple of years, we have been focused on three critical priorities; improving our execution to strengthen … Read More