– Lam reports another flat quarter & guide- No recovery in sight yet

– Seems like no expectation of recovery until 2025- Mixed results

– DRAM good- NAND weak- Foundry/Logic mixed-Mature weakening

– Clearly disappointing to investors & stock hoping for a chip recovery

Tag: tsmc

Intel High NA Adoption

On Friday April 12th Intel held a press briefing on their adoption of High NA EUV with Intel fellow and director of lithography Mark Phillips.

In 1976 Intel built Fab 4 in Oregon, the first Intel fab outside of California. With the introduction of 300mm Oregon became the only development site for Intel with large manufacturing, development,… Read More

Real men have fabs!

“Real men have fabs” was an insult AMD founder Jerry Sanders hurled at his poor competitors who could not afford to build fabs. A few years later, AMD would be fabless, spinning off its manufacturing facilities as GlobalFoundries. This was the beginning of a transformative period for the industry.

Lisa Su could rightfully retort:

TSMC and Synopsys Bring Breakthrough NVIDIA Computational Lithography Platform to Production

NVIDIA cuLitho Accelerates Semiconductor Manufacturing’s Most Compute-Intensive Workload by 40-60x, Opens Industry to New Generative AI Algorithms.

An incredible example of semiconductor industry partnerships was revealed during the Synopsys User Group (SNUG) last month. It started with a press release but there is much… Read More

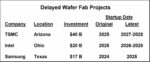

Semiconductor CapEx Down in 2024

U.S. President Biden announced on Wednesday an agreement to provide Intel with $8.5 billion in direct funding and $11 billion in loans under the CHIPS and Science Act. Intel will use the funding for wafer fabs in Arizona, Ohio, New Mexico, and Oregon. As reported in our December 2023 newsletter, the CHIPS Act provides a total of $52.7… Read More

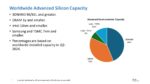

No! TSMC does not Make 90% of Advanced Silicon

Throughout the debate on fab incentives and the Chips Act I keep seeing comments like; TSMC makes >90% of all advanced silicon, or sometimes Taiwan make >90% of all advanced silicon. This kind of ill-defined and grossly inaccurate statement drives me crazy. I just saw someone make that same claim in the SemiWiki forums and… Read More

Intel and TSMC IDM 2024 Discussions

In December 2023, we published the Intel Revenue forecast for external wafer sales, gave a breakdown on how customers plan to ramp the foundry. The forecast is still valid (it assumes Intel executes on all plans) but since then we have a better understanding of Intel’s strategy and scenarios that could unfold.

The scenarios… Read More

International Women’s Day with Christelle Faucon VP Sales Agile Analog

Born in France, now living in the Netherlands, Christelle Faucon has over 25 years’ experience of working across the global semiconductor ecosystem. Currently she is VP of Sales at Agile Analog, the analog IP innovators. Following a Master’s Degree in Electronics Engineering, Christelle began her career as a Design Engineer.… Read More

Intel Direct Connect Event

On Wednesday, February 21st Intel held their first Foundry Direct Connect event. The event had both public and NDA sessions, and I was in both. In this article I will summarize what I learned (that is not covered by NDA) about Intel’s business, process, and wafer fab plans (my focus is process technology and wafer fabs).

Business

… Read MoreISS 2024 – Logic 2034 – Technology, Economics, and Sustainability

For the 2024 SEMI International Strategy Symposium I was challenged by members of the organizing committee to look at where logic will be in ten years from a technology, economics, and sustainability perspective. The following is a discussion of my presentation.

To understand logic, I believe it is useful to understand what makes… Read More