You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

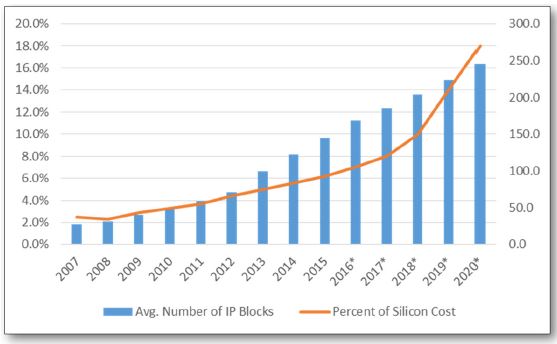

The recent growing complexity in SoC designs attributed to the increased use of embedded IP’s for more design functionalities, has imposed a pressing challenge to the post-silicon bring-up process and impacting the overall product time-to-market.

According to data from Semico Research, more than 60% of design starts contain… Read More

We have entered the age of AI specific processors, where specialized silicon is being produced to tackle the compute needs of AI. Whether they use GPUs, embedded programmable logic or specialized CPUs, many AI chips are based on parallel processing. This makes sense because of the parallel nature of AI computing. As a result, in… Read More

The automotive industry continues push the limits on how “smart” we can make our vehicles and from that, it follows as to how smart we can make the electronics in the vehicles. When I think of smart cars (and smart automotive ICs) I typically think of things like advanced driver-assistance systems (ADAS) that use AI and neural networks… Read More

Semiwiki readers are no doubt very familiar with the increasing impact of the automotive market on the semiconductor industry. The magnitude and complexity of the electronic systems that will be integrated into upcoming vehicle designs reflects the driver automation, safety, and entertainment features that are in growing… Read More

In the earliest days of IC design the engineering work was always done at the transistor-level, and then over time the abstraction level moved upward to gate-level, cell-level, RTL level, IP reuse, and high-level modeling abstractions. The higher levels of abstraction have allowed systems to be integrated into an SoC that can… Read More

Mentor has an especially strong position in the automotive space given their broad span of embedded, SoC, mechanical and thermal and system design tools. Of course, these days demonstrating ISO 26262 compliance is mandatory for semiconductor and systems suppliers, so EDA vendors need to play their part to support those suppliers… Read More

Layout-aware Diagnosisby Paul McLellan on 08-08-2014 at 8:01 amCategories: EDA

Traditional test methodologies have been based on the functional model, that is to say the netlist. The most well-known is probably the stuck-at model which grades a sequence of test vectors by whether they would have managed to notice the difference between a fully functional design and one where one of the signals was permanently… Read More

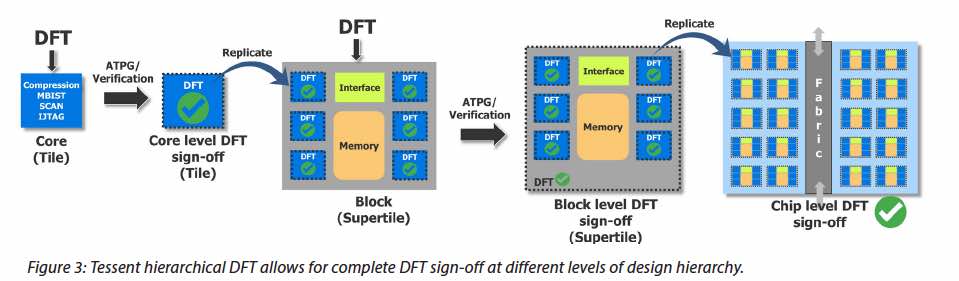

With the advent of large SoCs in semiconductor design space, verification of SoCs has become extremely challenging; no single approach works. And when the size of an SoC can grow to billions of gates, the traditional methods of testability of chips may no longer remain viable considering the needs of large ATPG, memory footprint,… Read More

You are cordially invited to have dinner with my favorite EDA CEO, Dr. Walden C. Rhines (the C stands for Clark by the way). Wally will be the dinner keynote speaker at the Electronic Design Process Symposium on April 17[SUP]th[/SUP] at the Yacht Club in Monterey. When registering use Promo Code: SemiWikiGofor $50 off. Such a deal!… Read More

As we move down into more and more advanced process nodes, the rules of how we test designs are having to change. One big challenge is the requirement to zoom in and fix problems by doing root cause analysis on test data alone, along with the rest of the design data such as detailed layout, optical proximity correction and so on. But without… Read More