A few months back, we interviewed Cristian Amitroaie, the CEO of AMIQ EDA. We talked mostly about their Design and Verification Tools (DVT) Eclipse Integrated Development Environment (IDE) and how it helps design and verification engineers develop code in SystemVerilog and several other languages. Cristian also mentioned… Read More

Tag: systemverilog

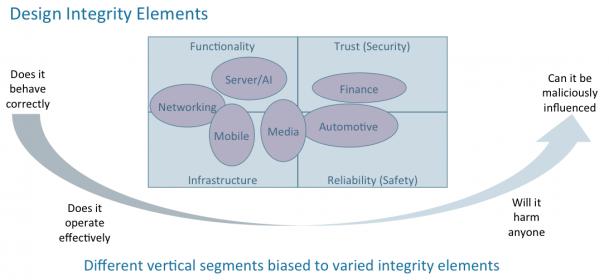

Portable Stimulus enables new design and verification methodologies

My usual practice when investing is to look at startup companies and try to understand if the market they are looking to serve has a significant opportunity for a new and disruptive technology. This piece compiles the ideas that I used to form an investment thesis in Portable Stimulus. Once collected, I often share ideas to get feedback.… Read More

CEO Interview: Cristian Amitroaie of AMIQ EDA

AMIQ EDA has caught my attention over the last few months. My first impression was that this was just another small IDE company trying to compete with established and bundled IDEs from the big 3, a seemingly insurmountable barrier. This view was challenged by an impressive list of testimonials, not just from the little guys but also… Read More

A Picture is worth a 1,000 words

Semiconductor IP re-use is a huge part of the productivity gains in SoC designs, so instead of starting from a clean slate most chip engineers are re-using cells, blocks, modules and even sub-systems from previous designs in order to meet their schedule and stay competitive in the market place. But what happens when you intend to… Read More

Getting More Productive Coding with SystemVerilog

HDL languages are a matter of engineering personal preference and often corporate policy dictates which language you should be using on your next SoC design. In the early days we used our favorite text-based editor like Vi or Emacs, my choice was Vi. The problem with these text-based editors of course is that they really don’t… Read More

Getting Ready for Bluetooth-5 Verification

Bluetooth has been very successful for many years, but arguably trapped in a niche, at least for us consumers, as a short-range wireless alternative to a wire connection – to connect your phone to a car or speakers for example. (In fairness I should add that the 4.2 version has improved range and Bluetooth has already become quite … Read More

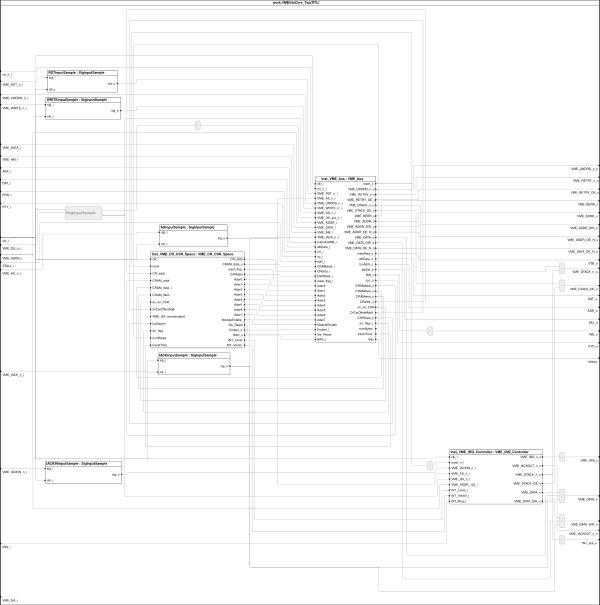

RTL Design Restructuring Explained

Modern SoC designs can use billions of transistors where transistors are grouped into gates, then gates grouped into cells, then cells grouped into blocks, blocks grouped into modules, and so on, creating a complex hierarchy. What a front-end designer conceives of logically for a hierarchy will differ from how an optimized physical… Read More

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

From Simulation to Emulation: 3 Steps to a Portable SystemVerilog/UVM Testbench

If your team is building large, complex designs that require millions of clock cycles to fully verify, you need both simulation and emulation.

Using emulation with simulation accelerates performance for dramatically reduced run times.… Read More

Webinar alert – VHDL guru says its time to move up

Many years ago when I worked for Ed Staiano at Motorola, I learned never to use the word “comfortable” in a career context. I’m comfortable being with family and friends. This new high-back chair I sit in at my new faux-cocobolo desk (slightly distressed chalk-painted wood and industrial piping, awesome) is comfortable,… Read More