FPGA’s have become an important part of system design. It’s a far cry from how FPGA’s started out – as glue logic between discrete logic devices in the early days of electronic design. Modern day FPGA’s are practically SOC’s in their own right. Frequently they come with embedded processor cores, sophisticated IO cells, DSP,… Read More

Tag: synplify

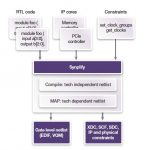

Four Steps for Logic Synthesis in FPGA Designs

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More

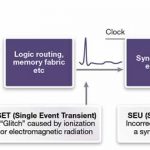

Did My FPGA Just Fail?

Designing DRAMs at Intel back in the 1970s I first learned about Soft Errors and the curious effect of higher failure rates of DRAM chips in Denver, Colorado with a higher altitude than Aloha, OR. With the rapid growth of FPGA-based designs in 2016, we are still asking the same questions about the reliability of our chips used for safety-critical… Read More

TMR approaches should vary by FPGA type

We’ve introduced the concepts behind triple modular redundancy (TMR) before, using built-in capability in Synopsys Synplify Premier to synthesize TMR circuitry into FPGAs automatically. A recent white paper authored by Angela Sutton revisits the subject… Read More

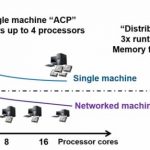

Why FPGA synthesis with Synplify is now faster

The headline of the latest Synopsys press release drops quite a tease: the newest release of Synplify delivers up to 3x faster runtime performance in FPGA synthesis. In our briefing for this post, we uncovered the surprising reason why – and it’s not found in their press release.… Read More

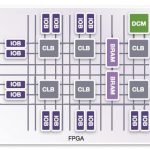

Dealing with FPGA IP in all its forms

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

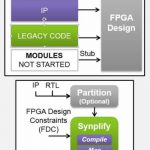

Conquering errors in the hierarchy of FPGA IP

FPGA design today involves not only millions of gates on the target device, but thousands of source files with RTL and constraints, often generated by multiple designers or third party IP providers. With modules organized in some logical way describing the design, designers brace themselves for synthesis and a possible avalanche… Read More

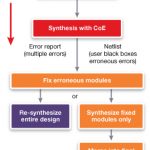

Second FPGA to the right, and straight on ‘til it works

In a fantasy world where there were no coding errors or integration issues, FPGA designs would fly straight through synthesis easily and quickly. Maybe that world does exist somewhere. For the rest of us, who have experienced the agony of running a large FPGA design – again – only to find another error and have to start over, there … Read More

FPGA Prototyping – What I learned at a Seminar

Intro

My first exposure to hardware prototyping was at Intel back in 1980 when the iAPX 432 chip-set group decided to build a TTL-based wire-wrap prototype of a 32 bit processor to execute the Ada language. The effort to create the prototype took much longer than expected and was only functional a few months before silicon came back.… Read More