If you want to remember the key points for Interface IP in 2021, just consider $1.3B, 22%, $3B. Interface IP category has generated $1 billion 300 million in 2021, or 22.7% year to year growth, thanks to high runner protocols PCIe, DDR memory controller and Ethernet/SerDes. Even more impressive is the forecast, as IPnest predict… Read More

Tag: synopsys

Casting Light on OpenLight’s Open Silicon Photonics Platform

For many decades now, modern optical technology has been deployed in networking infrastructure, for long haul and medium haul links to support internet communications. The foundation of this technology is photonics, which is the science of generation, manipulation and detection of light for performing functions otherwise… Read More

DesignDash: ML-Driven Big Data Analytics Technology for Smarter SoC Design

With time-to-market pressures ever increasing, companies are continually seeking enhanced designer productivity, faster design closure and improved project management efficiency. To accomplish these, organizations invest a lot in implementing both standardized approaches and proprietary techniques. With ever increasing… Read More

Very Short Reach (VSR) Connectivity for Optical Modules

Bandwidth, latency, power and reach are always the key points of focus when it comes to connectivity. As the demand for more data and higher bandwidth connectivity continue, power management is gaining a lot of attention. There is renewed interest in pursuing silicon photonics to address many of these challenges. There are many… Read More

Protecting High-Speed Interfaces in Data Centers with Security IP

The never ending appetite for higher bandwidths, faster data interfaces and lower latencies are bringing about changes in how data is processed at data centers. The expansion of cloud to the network edge has introduced broad use of artificial intelligence (AI) techniques for extracting meaning from data. Cloud supercomputing… Read More

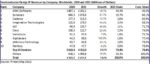

Design IP Sales Grew 19.4% in 2021, confirm 2016-2021 CAGR of 9.8%

Design IP Sales reached $5.45B in 2021, or 19.4% YoY after 16% in 2020, on-sync with semiconductor growth of 26.2% in 2021 according to WSTS. IPnest has released the “Design IP Report” in May 2022, ranking IP vendors by category (CPU, DSP, GPU & ISP, Wired Interface, SRAM Memory Compiler, Flash Memory Compiler, Library and I/O,… Read More

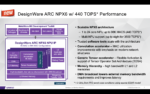

Bigger, Faster and Better AI: Synopsys NPUs

AI-based applications are fast advancing with evolving neural network (NN) models, pushing aggressive performance envelopes. Just a few years ago, performance requirements of NN driven applications were at 1 TOPS and less. Current and future applications in the areas of augmented reality (AR), surveillance, high-end smartphones,… Read More

The Path Towards Automation of Analog Design

You may have noticed that I have been writing a lot more about analog design lately. This is no accident. Analog and custom blocks are increasingly important because of the critical role they play in enabling many classes of systems, such as automotive, networking, wireless, mobile, cloud, etc. Many of the SoCs needed for these… Read More

Design to Layout Collaboration Mixed Signal

When talking about today’s sophisticated advanced node designs it’s easy to first think about the digital challenges. Yet, the effort to design the needed analog and mixed signal blocks for them should not be underestimated. The need for high speed clocks, high frequency RF circuits and high bit rate IOs makes the analog portions,… Read More

Synopsys Announces FlexEDA for the Cloud!

There’s been a lot of discussion and hype regarding use of the cloud for chip design for quite a while, more than ten years I would say. I spoke with Synopsys to better understand their recent Synopsys Cloud announcement to determine if it is different. Briefly, it is different, and here is why:

If you’re trying to design a complex SoC,… Read More