An increasing percentage of SoC die area is being allocated to memory arrays, as applications require more data/instruction storage and boot firmware. Indeed, foundries invest considerable R&D resources into optimizing their array technology IP offerings, often with more aggressive device features than used for other… Read More

Tag: soc

Reusable HW/SW Interface for Portable Stimulus

Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

Arteris Unveils Solution for Heterogeneous Cache Coherent SOC’s

Designing SOC’s for markets like automotive and mobile electronics requires taking advantage of every opportunity for optimization. One way to do this is through building a cache coherent system to boost speed and reduce power. Recently, NXP decided to go about this on their automotive MCU based SOC’s by using Arteris’ just-announced… Read More

DRC Concept for IP Qualification and SoC Integration

In the history of semiconductor design and manufacturing, the age-old concept of DRC rule-deck qualification for handshake between design and manufacturing still applies strongly to produce working silicon. In fact, DRC clean GDSII works as the de facto golden gate between a design and a foundry for manufacturing the chip for… Read More

The Xiaomi Redmi Note 3 Significantly Improves Performance

The smartphone market has been experiencing many changes, some of those changes have included the slowing of the overall pace of growth. One of the remaining growth segments of the smartphone market right now remains the mid-range which is priced around $200. These phones have traditionally been ignored by the big players in the… Read More

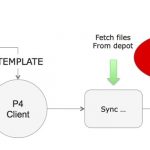

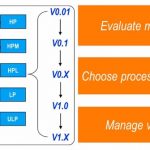

Bulking Up of Design Data Calls for Version Control on Steroids

Even though design management systems are gaining popularity as a way to manage design data growth, they actually contribute to the problem of exploding data size. What we already know is that a linear increase in die size causes exponential growth in chip area, and that smaller feature sizes compound this effect in the same way.… Read More

CEO Insight: Transformation of Vayavya Labs into System Design Automation

With the advent of SoCs, design abstractions and verification has moved up at the system level. It’s imperative that EDA moves up the value chain to start design automation at system level. The System Design Automation will be the new face of EDA in coming years.… Read More

How to Deal With Seven Design Closure Issues

The challenge of tracking design progress is a shared problem for individual designers, team leaders, and project managers. At each level the ability to step back from just reviewing error log files and seeing the arc of the whole design as it moves forward is valuable. The difficulty of seeing the whole picture is exacerbated when… Read More

Process Development, CAD and Circuit Design

Working at Intel as a circuit designer I clearly remember how there were three distinct groups: Process Development, CAD and Circuit Design. Each of the groups sat in a different part of the building in Aloha Oregon, we had different job titles, different degrees, spoke with different acronyms and yet we all had to work together … Read More

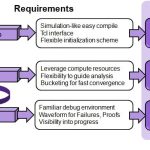

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More