Fractal Technologies is a privately held EDA company with offices in San Carlos, California and Eindhoven, the Netherlands. The company was founded by a small group of highly recognized EDA professionals. The scope of Fractal Technologies is to check consistency and validate all different data formats used in your design and… Read More

Tag: semiconductors

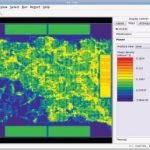

The Ugly Stepchild of Physical Verification – Thermal!

Thermal analysis has traditionally been given short shrift when compared to other more prominent issues facing chip designers. Invarian, to my eye at least, feels that the winds of change are in the air. Not that power or EM/IR issues will fade, that indeed is not the case and in fact quite the contrary, they are contributors to the… Read More

SemiWiki Top 10 Must See @ #50DAC List!

This list was compiled by the SemiWiki bloggers highlighting emerging technologies that we have written about and that will be demonstrated at the Design Automation Conference next week. We highly recommend you investigate them further during your time in Austin and please let us know what you think.

Today SemiWiki has more than… Read More

TSMC ♥ Berkeley Design Automation

As I mentioned in BDA Takes on FinFET Based Memories with AFS Mega:

Is AFS Mega real? Of course it is, I’m an SRAM guy and I worked with BDA on this product so I know. But don’t take my word for it, stay tuned for endorsements from the top SRAM suppliers around the world.

Here is the first customer endorsement from the #1 foundry.… Read More

Advanced Verification – HW/SW Emulation – SoC/ASIC Prototyping

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. With an active user community of over 35,000, 50+ global partners, offices worldwide… Read More

The Hot Zone: Do Good While Having Fun

The big 50th Anniversary party for DAC is on Monday night at the home of Austin City Limits. However, you can do good while enjoying yourself and also get into “The Hot Zone”, an exclusive area within the party in the penthouse Jack and Jim Gallery. The Gallery features 30 original photographs from the godfather of music… Read More

AMS Design, Layout and Verification @ #50DAC

Competition in EDA is absolutely necessary in order for the fabless semiconductor ecosystem to thrive. AMS tools with a low learning curve, high interoperability, and a powerful user interface improve design team productivity and enable a low total cost of ownership. That is why Tanner EDA has shipped over 33,000 licenses of … Read More

Transistor-Level Update from Cadence at DAC

My 8 years as an IC circuit designer were at the transistor-level, so if that interests you as well then consider what there is to see from Cadence at DAC this year. IC design technology is changing quickly, so keeping up to date is important for your job security and continual education goals.

Here’s what I would recommend attending… Read More

Design Data Management – Key Winning Strategy!

In a complex semiconductor market today, characterized by ever increasing design size and complexity, long design cycle, rapid technological advancement, intense competition, pricing pressure, small window of opportunity, development and cross-functional teams spread across the globe and multiple design partners including… Read More

BDA Introduces High-Productivity Analog Characterization Environment (ACE)

Last week Berkeley Design Automation introduced a new Analog Characterization Environment (ACE) – a high-productivity system to ensure analog circuits meet all specifications under all expected operational, environmental, and process conditions prior to tapeout.

While standard cell characterization and memory characterization… Read More