Selectively automating non-critical aspects of custom IC design allows engineers to focus on precision-crafting their designs. Cadence circuit design solutions enable fast and accurate entry of design concepts, which includes managing design intent in a way that flows naturally in the schematic. Using this advanced, parasitic-aware… Read More

Tag: semiconductor

MemCon Returns

Back before Denali was acquired by Cadence they used to run an annual conference called MemCon. Since Denali was the Switzerland of EDA, friend of everyone and enemy of none, there would be presentations from other memory IP companies and from major EDA companies. For example, in 2010, Bruggeman, then CMO of Cadence, gave the opening… Read More

How Many Licenses Do You Buy?

An informal survey of RTDA customers reveals that larger companies tend to buy licenses based on peak usage while smaller companies do not have that luxury and have to settle for fewer licenses than they would ideally have and optimize the mix of licenses that they can afford given their budget. Larger companies get better prices… Read More

Libraries Make a Power Difference in SoC Design

At Intel we used to hand-craft every single transistor size to eek out the ultimate in IC performance for DRAM and graphic chips. Today, there are many libraries that you can choose from for an SoC design in order to reach your power, speed and area trade-offs. I’m going to attend a Synopsys webinar on August 2nd to learn more … Read More

EUV: No Pellicle

There’s a dirty secret problem about EUV that people don’t seem to to be talking about. There’s no pellicle on a EUV mask. OK, probably you have no idea what that means, a lot of jargon words, nor why it would be important, but it seems to me it could be the killer problem for EUV.

In refractive masks, you print a pattern… Read More

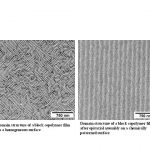

Directed Self Assembly

At Semicon, Ben Rathsack of Tokyo Electron America talked about directed self assembly (DSA) at the standing-room only lithography morning. So what is it? Self assembly involves taking two monomers that don’t mix and letting them polymerise (so like styrene forming polystyrene). Since they won’t mix they will … Read More

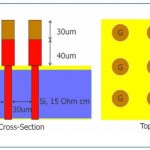

How Do You Extract 3D IC Structures?

The press has been buzzing about 3D everything for the past few years, so when it comes to IC design it’s a fair question to ask how would you actually extract 3D IC structures for use by analysis tools like a circuit simulator. I read a white paper by Christen Decoin and Vassilis Kourkoulos of Mentor Graphics this week and became… Read More

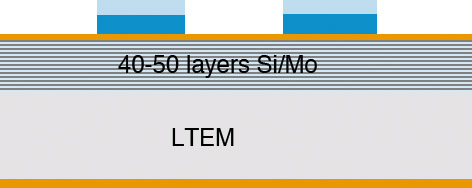

EUV Masks

This is really the second part to this blog about the challenges of EUV lithography. The next speaker was Franklin Kalk who is CTO of Toppan Photomasks. He too emphasized that we can make almost arbitrarily small features but more and more masks are required (not, that I suspect, he would complain being in the mask business). For EUV… Read More

Design-to-Silicon Platform Workshops!

Have you seen the latest design rule manuals? At 28nm and 20nm design sign-off is no longer just DRC and LVS. These basic components of physical verification are being augmented by an expansive set of yield analysis and critical feature identification capabilities, as well as layout enhancements, printability, and performance… Read More

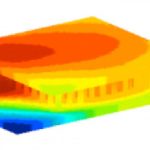

3D Thermal Analysis

Matt Elmore of ANSYS/Apache has an interesting blog posting about thermal analysis in 3D integrated circuits. With both technical and economic challenges at process nodes as we push below 28nm, increasingly product groups are looking towards through-silicon-via (TSV) based approaches as a way of keeping Moore’s law… Read More