You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Jasper is presenting at both ends of the world at both ends of February.

First in Israel, it is SemiIsrael Verification Day 2013 on February 5th (next Tuesday) at Green House in Tel Aviv.

- Zihad Hanna, VP of Research and Chief Architect and General Manager of Jasper Israel will be talking about Security Formal Verification of Hardware

…

Read More

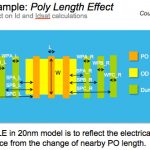

I already talked about how Cadence is splitting Virtuoso into two. Anyway, it is now officially announced. The 6.1 version will continue to be developed as a sort of Virtuoso classic for people doing designs off the bleeding edge that don’t require the new features. And a new Virtuoso 12.1 intended for people doing 20nm and… Read More

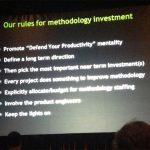

I was at DesignCon in Santa Clara today and listened to Jonah Alben of NVIDIA’s keynote on what their approach is to improving design methodology. He started by pointing out that most companies underinvest in EDA (and he includes NVIDIA in this). Partially it is complaceny: that last chip taped out so we know we can do it again.… Read More

While the SPIE Advanced Lithography conference is best known for IC manufacturing, computational lithography, mask preparation and other back-end topics, there is also a significant amount of interest in Design for Manufacturing (DFM) at the conference because some litho issues are best (or only) addressed by modifying the… Read More

The Linley Group’s Microprocessor conference in Spring is focused on Datacenters now that cloud computing and massive internal datacenters has made them so important. The conference is on February 5th and 6th. It is free to qualified people such as network equipment vendors, network service providers and so on (which … Read More

I sat down last week for lunch with Michael Sanie. Mike and I go back a long way, working together at VLSI Technology (where his first job out of school was to take over the circuit extractor that I’d originally written) and then in strategic marketing at Cadence. Now Mike has marketing for (almost?) all of Synopsys’s … Read More

Over at the GSA Forum website I have an article on the history of the semiconductor industry. It is actually based on a couple of brief history of semiconductor blogs (here and here) I published here on SemiWiki last year but edited down a lot and tightened up.

Since the start of the year seems to be the time for predictions, here are the… Read More

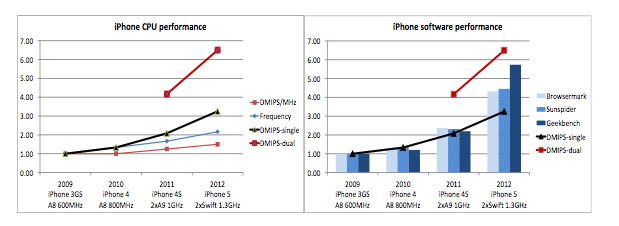

This is the second blog entry about an ST Ericsson white-paper on multiprocessors in mobile. The first part was here.

The first part of the white-paper basically shows that for mobile the optimal number of cores is two. It is much better to use process technology (and good EDA) to run the processor at higher frequency rather than add… Read More

I came across an interesting white-paper from ST Ericsson on two topics: multi-processors in mobile platforms and FD-SOI. FD-SOI is the ST Microelectronics alternative to FinFETs for 20nm and below. It stands for Fully-Depeleted Silicon-on-Insulator. But I’m going to save that part of the white-paper for another blog… Read More

Oasys Has a New CEOby Paul McLellan on 01-18-2013 at 2:21 pmCategories: EDA

Scott Seaton is the new CEO of Oasys Design Systems. Paul van Besouw, the CEO since the company’s founding, becomes the CTO. I met Scott last year when I was doing some consulting work for Carbon Design where he was VP of sales (the new VP sales at Carbon is Hal Conklin, by the way).

I talked to Scott about why he had joined Oasys. … Read More