The decision made by United States Court of Appeals for the Federal Circuit, “Affirming” the District Court for the Northern District of California’s summary judgment of non-infringement on Kilopass’ patent claims and its dismissal, with prejudice, of all remaining claims against Sidense, is certainly a good news for IP and… Read More

Tag: semiconductor

Denali+Tensilica+Cosmic = Cadence

I won’t be able to attend Chris Rowen’s presentation here at the GlobalPress Electronic Summit since I’m going to the first day of the Linley Mobile Microprocessor conference. In fact I wonder if Chris himself will make it since he was running in the Boston marathon on Monday. He finished about 10 minutes before… Read More

Atrenta, Forte and Jasper LOVE DAC

I LOVE DAC is back. This year the sponsors are Atrenta, Jasper and Forte (hey, all semiwiki subscribers). The way it works is that you register on the DAC website here and you get a free three-day exhibit pass. In addition to everything going on in the exhibit hall, including the pavilion panels held there, the pass also gives access… Read More

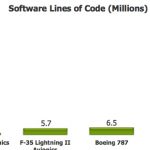

Wally Rhines: Embedded Software the Next Revolution?

As seems to be traditional, Wally Rhines gave a keynote here at the GlobalPress Electronics Summit here in sunny Santa Cruz. It was entitled Embedded Software, the Next Revolution in EDA. Unlike Cadence and Synopsys, Mentor has a strong position in embedded software. It has been build up over a long time through a series of acquisitions… Read More

Cavendish Kinetics

I have spent the last couple of days at the GlobalPress Electronics Summit at the Chaminade Resort in Santa Cruz. Hey, it’s tough, but someone has to do it. One interesting presentation was from Cavendish Kinetics. It is especially interesting because many years ago Cavendish was founded by Mike Beunder, who I know well since… Read More

Xilinx: Hide the RTL

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More

Altera, Intel, TSMC, ARM: the Plot Thickens

Vince Hu of Altera presented us her at the GlobalPress Electronics Summit on their process roadmap. Since just a month or two ago they announced that Intel would be their foundry at 14nm, everyone wanted to get a better idea of what was really going on.

At 28nm, Altera use 2 processes, TSMC 28HP (for high end Stratix-5 devices) and TSMC… Read More

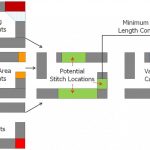

Chasing DP Rabbits

“Now, here, you see, it takes all the running you can do, to keep in the same place. If you want to get somewhere else, you must run at least twice as fast as that!”

—Lewis Carroll, Through the Looking Glass

The use of stitching can greatly reduce the number of double patterning (DP) decomposition violations that a designer has to resolve.… Read More

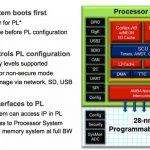

Ivo Bolsens’ Keynote on the All-Programmable SoC

Ivo Bolsens, the CTO of Xilinx, is giving the opening keynote at the Electronic Design Process Symposium (EDPS) in Monterey on Thursday and Friday this coming week. The title of his keynote is The All Programmable SoC – At the Heart of Next Generation Embedded Systems. He covers a lot of ground but the core of his presentation… Read More

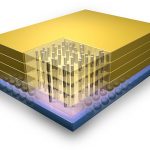

3D IC: Are We There Yet?

For the last few years, thru silicon via (TSV) based ICs have been looming in the mist of the future. Just how far ahead are they? Xiliinx famously has a high-end gate-array in production on a 2.5D interposer, Micron has a memory cube, TSMC has done various things in 3D that it calls CoWoS (chip on wafer on substrate), Qualcomm have been… Read More