You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At Semicon Japan a few days ago, Subi Kengeri of GlobalFoundries delivered the keynote. While he covered a number of topics, using Tokyo’s recent win of the 2020 Olympics as a hook, one major theme was the increasing importance of processes other than the bleeding edge digital processes that get all the news.

What is leading… Read More

Yesterday Cadence had their annual front-end summit, the theme of which was physically aware design. I was especially interested in the first couple of presentations about physically aware synthesis. I joined Cadence in 1999 when they acquired Ambit Design Systems. One of the products that we had in development was called PKS… Read More

Two conferences on 3D, one just over and one coming up next week. The one that was just over was hosted by Georgia Tech, the 3rd Annual Global Interposer Technology Workshop (GIT). I wasn’t there but my ex-colleague from VLSI Technology Herb Reiter was. Herb has become very much associated with all things 3D since he led the … Read More

I came across an interesting article by Will Strauss which is pretty much the history of DSP in communication chips. Having lived through the early part of the history while I was at VLSI Technology I found it especially interesting.

At VSLI, our first GSM (2G, i.e. digital not analog air interface) was a 5-chip chipset. The DSP functionality… Read More

To the surprise of nearly all observers and due to no extraordinary technological advancement, there is one true mobile winner of the past year and that is Micron, whose stock has soared in 2013 from $5 to $21. I know, you’re probably saying, “Micron, you can’t be serious.” Let’s run through the … Read More

The first part of Lars Liebmann’s ICCAD keynote about lithography was on the changes in lithography that have to us to where we are today. In some ways it was an explanation of why we have the odd design rules, double patterning etc that we have in 20nm and 16nm processes. The second part of his talk was a look forward to how we might… Read More

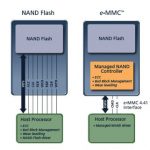

eMMC Mobile Memoryby Paul McLellan on 11-27-2013 at 11:40 amCategories: Arasan, IP

eMMC is the standard for mobile memory used in smartphones and tablets. The latest standard, released just this year, is eMMC 5.0. The previous standard, 4.51, was only released last year so things are moving quickly.

Arasan have a webinar next week to bring you up to speed on eMMC 5.0 in general and, of course, their own IP offering… Read More

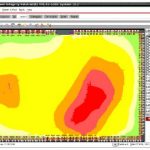

Yesterday Cadence had an all-day Signoff Summit where they talked about the tools that they have for signoff in advanced nodes. Well, of course, those tools work just fine in non-advanced nodes too, but at 20nm and 16nm there are FinFETs, double patterning, timing impacts from dummy metal fill, a gazillion corners to be analyzed… Read More

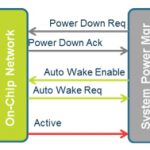

If it has escaped your notice that power management on SoCs is important then you need to get out more. Increasingly, the complexity of the interconnect between the various processors, memories, offload processors, devices, interfaces and other blocks means that the best way to implement it is to use a network on chip (NoC). But… Read More

Today at the Semisrael Expo 2013 (in Israel of course) Ajoy Bose gave a keynote on how design methodology will impact electronics. The big pictures is that microelectronics is driven by some major disruptive forces and, as a result, technology and industry are evolving dramatically, which creates a need for research and innovation… Read More