In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

Tag: schematic

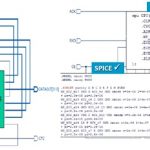

Expert Tool to View and Debug Design Issues at Spice Level

Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

Enabling Higher Level Design Automation with Smart Tools

Although design houses have always strived for optimizing best design flows according to their design needs by customizing the flows using effective and efficient internal as well as external tools, this need has further grown in the context of design scenarios getting wider and wider from transistor, gate and RTL to system level.… Read More

S-engine Moves up the Integration of IPs into SoCs

As the semiconductor design community is seeing higher and higher levels of abstraction with standard IPs and other complex, customized IPs and sub-systems integrated together at the system level, sooner than later we will find SoCs to be just assemblies of numerous IPs selected off-the-self according to the design needs and… Read More

A New, Free, Web-Based EDA Toolset in the Cloud

In the 1990’s there was a push to build EDA frameworks, however they all failed because no user wanted to be locked into one EDA vendor tool flow. Fast forward to 2014 and there’s an emerging trend to use web-based EDA tools as a framework, instead of downloading and installing software to your desktop or device. I just… Read More

Mixed-Signal SoC Debugging & IP Integration Made Easy

A semiconductor SoC design can have multiple components at different levels of abstractions from different sources and in different languages. While designing an SoC, IPs at different levels have to be integrated without losing the overall design goals. Of course, quality of an IP inside and outside of an SoC must be tested thoroughly.… Read More

What Makes A Designer’s Day? A Bottleneck Solved!

In an environment of SoCs with tough targets of multiple functionalities, smallest size, lowest power and fastest performance to achieve within a limited design cycle window in order to meet the rigid time-to-market requirements, any day spent without success becomes very frustrating for a designer. Especially during tape-out… Read More

Develop A Complete System Prototype Using Vista VP

Yes, it means complete hardware and software integration, debugging, verification, optimization of performance and power and all other operational aspects of an electronic system in semiconductor design. In modern SoCs, several IPs, RTL blocks, software modules, firmware and so on sit together on a single chip, hence making… Read More