I had the opportunity to preview an upcoming webinar from Synopsys on SoC Glitch Power – what it is and how to reduce it. There is some eye-opening information in this webinar. Glitch power is a bigger problem than you may think and Synopsys has some excellent strategies to help reduce the problem. The webinar is available via replay… Read More

Tag: rtl

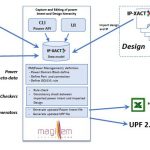

Magillem offers a practical UPF power flow

We already know that IP-Xact is extremely useful for managing IP and SOC design specifications, yet it may come as a surprise to learn that it also can be used to form the basis of a power flow too. There are design tools that read UPF to help implement and verify designs, however it can be extremely useful to understand the interplay … Read More

The Practice of Low Power Design

For any given design objective, there is what we in the design automation biz preach that design teams should do, and then there’s what designs teams actually do. For some domains, the gap between these two may be larger than others, but we more or less assume that methodologies which have been around for years and are considered to… Read More

Clock Gating Optimization

You can save a lot of power in a design by gating clocks. For much of the time in a complex multi-function design, many (often most) of the clocks are toggling registers whose input values aren’t changing. Which means that those toggles are changing nothing functionally yet they are still burning power. Why not turn off those clock… Read More

Analysis and Signoff for Restructuring

For the devices we build today, design and implementation are unavoidably entangled. Design for low-power, test, reuse and optimized layout are no longer possible without taking implementation factors into account in design, and vice-versa. But design teams can’t afford to iterate indefinitely between these phases, so they… Read More

Open-Silicon Update: 125M ASICs shipped!

As you all know I am a big fan of the ASIC business model. It was critical in the transformation of the fabless semiconductor industry and still plays a critical part in our success. In fact, the ASIC business model is leading the way for systems companies to make their own chips. Remember, Apple started with the ASIC business model … Read More

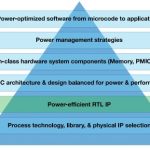

How ARM designs and optimizes SoCs for low-power

ARM has become such a worldwide powerhouse in delivering processors to the semiconductor IP market because they have done so many things well: IP licensing model, variety, performance, and low-power. On my desk are two devices with ARM IP, a Samsung Galaxy Note 4 smart phone and a Google tablet. Most of my readers will likely have… Read More

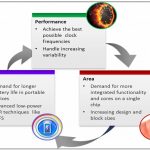

How to nail your PPA tradeoffs

How do you ensure your design has been optimized for power, performance, and area? I posed this question to Mentor’s Group Director of Marketing, Sudhakar Jilla and product specialist Mark Le. They said that finding the PPA sweet spot is still often done by trial and error – basically serial experiments with various input parameters… Read More

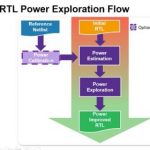

Achieving Lower Power through RTL Design Restructuring (webinar)

From a consumer viewpoint I want the longest battery life from my electronic devices: iPad tablet, Galaxy Note 4 smart phone, Garmin Edge 820 bike computer, and Amazon Kindle book reader. In September I blogged about RTL Design Restructuring and how it could help achieve lower power, and this month I’m looking forward to … Read More

A Credible Player at the Power Table

For a while it seemed like Mentor lived on the margins of the (RTL) design-for-power game. They had interesting micro-architectural optimization capabilities through their Calypto heritage but no real industry chops in power estimation, a must-have when you are claiming to reduce power. Better known offerings in RTL power … Read More