As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Tag: redhawk

Reliability sign-off has several aspects – One Solution

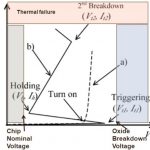

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More

Power and Reliability Sign-off – A must, but how?

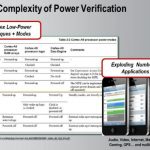

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

Full Chip IR Drop Analysis using Distributed Multi Processing

IR drop analysis across your board, package and SoC ensures that your Power Delivery Network (PDN) is robust, and that your system will function to spec. There are both static and dynamic approaches to IR drop analysis of a full-chip with billions of transistors, while the dynamic approach produces the most accurate results compared… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

Samsung’s Life of Pi @ Apache @ DAC

Last week I talked to Eileen You of Samsung-SSI to get a preview on what they will be talking about at Apache’s customer theater at DAC. Their presentation is titledThe Life of PI: SoC Power Integrity from Early Estimation to Design Sign-off. The ‘PI’ stands for Power Integrity.

Samsung-SSI’s operations… Read More

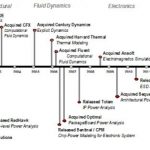

A Brief History of Apache Design

Apache Design Solutions was founded in 2001 by Andrew Yang and three researchers from HP Labs (Norman Chang, Shen Lin, Weize Xie). They realized that engineers striving to meet the goal of increased device miniaturization, as defined by Moore’s Law, would eventually hit stumbling blocks in their progress. The founding team believed… Read More

Apache Power Artist Capabilities II

This is the second part of my discussion with Paul Traynar, Apache’s PowerArtist guru. The first part discussed sequential reduction capabilities. Part I was here.

There are two big challenges with doing power analysis at the RTL level. Firstly, how do you get an accurate enough model of what the design will dissipate given… Read More

Chip-Package-System Solution Center

One of the really big changes about chip design is the way over the last decade or so it is no longer possible to design an SoC, a package for it to go in and the board for the package using different sets of tools and methodologies and then finally bond out the chip and solder it onto the board. The three systems, Chip-Package-System have… Read More

Apache Low Power Webinars

For those of you who didn’t get to DAC you can catch up on low power issues with Apache’s series of low-power webinars taking place late in July. All webinars are at 11am Pacific Time. Full details and registration on the Apache website here.… Read More