As analog and mixed-signal designs become increasingly complex, parasitic effects dominate both design time and cost, consuming 30–50% of engineers’ effort in debugging and reanalyzing circuits. Addressing these multiphysics effects requires early verification strategies and reliable simulation solutions. Modern … Read More

Tag: redhawk-sc

Unleash the Power: NVIDIA GPUs, Ansys Simulation

In the realm of engineering simulations, the demand for faster, more accurate solutions to complex multiphysics challenges is ever-growing.

Simulation is a vital tool for engineers to design, test, and optimize complex systems and products. It helps engineers reduce costs, improve quality, and accelerate innovation. However,… Read More

Ansys’ Emergence as a Tier 1 EDA Player— and What That Means for 3D-IC

Over its 40+ year history, electronic design automation (EDA) has seen many companies rise, fall, and merge. In the beginning, in the 1980s, the industry was dominated by what came to be known as the big three — Daisy Systems, Mentor Graphics, and Valid Logic (the infamous “DMV”). The Big 3 has morphed over the years, eventually settling… Read More

Multiphysics, Multivariate Analysis: An Imperative for Today’s 3D-IC Designs

Semiconductor manufacturers are under constantly increasing and intense pressure to accelerate innovative new chip designs to market faster than ever in smaller package sizes while assuring signal integrity and reducing power consumption. Three-dimensional integrated circuits (3D-ICs) promise to answer all these demands… Read More

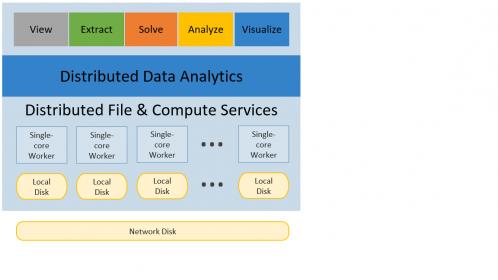

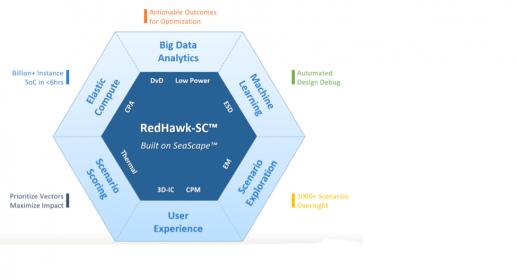

Analytics and Visualization for Big Data Chip Analysis

Designers require comprehensive logical, physical, and electrical models to interpret the results of full-chip power noise and electromigration analysis flows, and subsequently deduce the appropriate design updates to address any analysis issues. These models include: LEF, DEF, Liberty library models (including detailed… Read More

Big Data Analytics and Power Signoff at NVIDIA

While it’s interesting to hear a tool-vendor’s point of view on the capabilities of their product, it’s always more compelling to hear a customer/user point of view, especially when that customer is NVIDIA, a company known for making monster chips.

A quick recap on the concept. At 7nm, operating voltages are getting much closer… Read More

Big Data and Power Integrity: Drilling Down

I’ve written before about how Ansys applies big data analytics and elastic compute in support of power integrity and other types of analysis. A good example of the need follows this reasoning: Advanced designs today require advanced semiconductor processes – 16nm and below. Designs at these processes run at low voltages, much… Read More

Margin Call

A year ago, I wrote about Ansys’ intro of Big Data methods into the world of power integrity analysis. The motivation behind this advance was introduced in another blog, questioning how far margin-based approaches to complex multi-dimensional analyses could go. An accurate analysis of power integrity in a complex chip should… Read More