You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

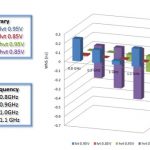

GLOBALFOUNDRIES has been evangelizing their 22FDX FD-SOI process for a few months; readers may have seen Tom Simon’s write-up of their preview at ARM TechCon. Dr. Joerg Winkler recently gave an updated webinar presentation of their approach in an implementation of ARM Cortex-A17 core.

By now, you’ve probably heard that 22FDX… Read More

If we look back in the last century, performance and area were two main criteria for semiconductor chip design. All design tools and flows were concentrated towards optimizing those two aspects. As a result, density of chips started increasing and power became a critical factor. Now, Power, Performance and Area (PPA) are looked… Read More

Yesterday was the first day of CDNLive. There were three keynotes. The first was by Lip-Bu Tan, Cadence’s CEO (and the Chairman of Walden International that he will be the first to remind you). The most interesting tidbit was that Cadence now has over 1000 people working on IP and that it represents 11% of their revenue. Then… Read More

Semiconductors have played very important role in making internet successful and that has unleashed the potential of e-commerce. Today, we see names like Alibaba, whose primary focus is on commodity trade. I couldn’t imagine an e-commerce type of web portal for semiconductor services until I looked at the eSilicon website. … Read More

I think by now all of us know, or have heard about 20nm process node, its PPA (Power, Performance, Area) advantages and challenges (complexity of high design size and density, heterogeneity, variability, stress, lithography complexities, LDEs and so on). I’m not going to get into the details of these challenges, but will ponder… Read More

Oasys Bakes a PIEby Paul McLellan on 07-17-2013 at 3:01 pmCategories: EDA

One challenge in building a modern SoC is that you want to minimize power, performance and area (PPA) while still getting your chip to market on schedule. Realistically, you can’t actually minimize all of these at once since they are tradeoffs: speeding up a critical path often involves upsizing drivers to larger cells which… Read More