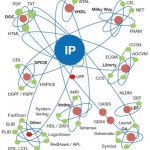

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

Tag: power

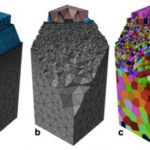

The Transistor is the Foundation of TCAD to Signoff

At the most basic level, semiconductor design is all about transistors. Any report on a large microprocessor or mobile application processor is in awe about how many transistors it contains. Moore’s Law is all about the most economic way to manufacture transistors. Each process generation for the last decade and looking ahead… Read More

High-Voltage Power Design

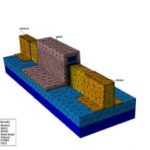

Most of what is talked about on SemiWiki is silicon design. After all for regular SoCs it is the only game in town. But for high voltage power applications (think automotive for one big market) there are other more esoteric technologies becoming more attractive.

Silicon has been the material of choice for high-voltage power applications… Read More

A Key Partner in the Semiconductor Ecosystem

Often we hear about isolated instances of excellence from various companies in the semiconductor industry which contribute significantly in building the overall ecosystem. While the individual excellence is essential, it’s rather more important how that excellence is utilized in a larger way by the industry to create a ‘value… Read More

Is Low Power a Challenge? ICE-Grain Answers the Challenge

Blogs have limited wordcount so insert your own generic opening paragraph here about the importance of low power in IC design. Mention IoT and cloud datacenters for extra credit.

It is well-known that the biggest reductions in power come from changes at the architectural level. Tools and process can do some things and since they… Read More

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

Silvaco: TCAD to Signoff in Vertical Markets

Recently, I talked about meeting with Dave Dutton the CEO of Silvaco. Mainly we were talking about the recent acquisition of Invarian but he also brought me up to date on Silvaco and how he is bringing their disparate product lines into a more focused strategy.

See also Silvaco Swallows Invarian

Silvaco would be the first to admit … Read More

Sensing Without (much) Power

Do you have one of those step-tracker things? They seem to be one of the earliest IoT devices that are actually selling in large quantities. Smartphones are also starting to contain this sort of sensor to provide similar functionality without requiring a separate device, as are smart-watches such as the Jumpy watch for kids on the… Read More

SoCs in New Context Look beyond PPA

If we look back in the last century, performance and area were two main criteria for semiconductor chip design. All design tools and flows were concentrated towards optimizing those two aspects. As a result, density of chips started increasing and power became a critical factor. Now, Power, Performance and Area (PPA) are looked… Read More

Getting a Grip on the Internet of Things

QuickLogic’s CTO Tim Saxe gave a keynote Getting a Grip on the Internet of Things at the IoT Summit last week.

He started by relating how things have changed over the last 3 years when he talks to customers.

- Three years ago it was sensor hubs in smartphones and the power budget was 3mW (so one day between re-charging, something