If you have read the white paper recently launched by Dolphin, “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, you should already know about the theory. This is a good basis to go further and discover some real-life examples, like Bluetooth Low Energy (BLE) chip in … Read More

Tag: power domain

A Tool Conceived With Designers’ Input and Developed from Scratch

If we look at the past, most of the EDA tools in the semiconductor design space have originated from a designers’ need to do things faster. Regardless of whether it is design exploration, manual design, simulation, verification, optimization (Power Performance Area – PPA) and many other steps in the overall design flow.… Read More

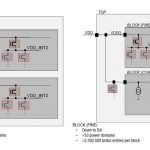

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

Stick to the script for repeatable FPGA-based prototyping

70% of today’s ASIC and SoC designs are being prototyped on FPGAs. Everybody knows that. But, did you know that automating the process of converting what could be thousands of ASIC “golden” files into FPGA-friendly versions can mean big savings in a large design?… Read More

Robust Design <- Robust Flow <- Robust Tools

I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More