Mike Gianfagna, a fellow SemiWiki blogger and a one-time colleague at Atrenta shared a useful piece of marketing advice. If your company is not the biggest fish in the pond and you want to appear more significant, team up with other companies to put on an event, say a webinar. Pick your partners so that you can jointly offer a larger,… Read More

Tag: pcie

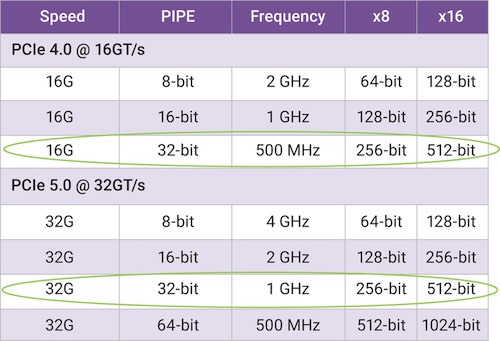

PCI Express in Depth – Physical Layer

In the last article, I wrote about the PCIe basic concepts. This article will reach the physical layer of the PCIe standard.

The lowest PCI Express architectural layer is the Physical Layer. This layer is responsible for actually sending and receiving all the data to be sent across the PCI Express link. The Physical Layer interacts… Read More

PCI Express in Depth

This is another post that was requested by a user, and as always i’ll do my best to put in a few articles the basic information that you’ll need to understand how it works at depth level.

PCI Express (or PCIe) is a high-speed serial computer expansion bus designed to replace the older PCI, PCI-X and AGP standards.

The first… Read More

A VIP to Accelerate Verification for Hyperscalar Caching

Non-volatile memory (NVM) is finding new roles in datacenters, not currently so much in “cold storage” as a replacement for hard disk drives, but definitely in “warm storage”. Warm storage applications target an increasing number of functions requiring access to databases with much lower latency than is possible through paths… Read More

Synopsys is First IP Provider with a Complete CXL Implementation Available

Synopsys just announced the availability of their IP solution supporting CXL (Compute Express Link). This new protocol is going to be an important component for several applications expected to be shipping starting in 2021. CXL is an alternate protocol that runs on the same physical layer as PCI Express (PCIe). Among other usages,… Read More

Silvaco Samsung and Excitement at 56thDAC

There were quite a few announcements at the Samsung Foundry Forum but my favorite was the IP partnership between Samsung and Silvaco. IP is a critical part of the fabless ecosystem and one of the advantages an IDM foundry has over a pure-play is the vast amounts of internal IP that have been silicon proven over the years. With Samsung… Read More

PCIe 5.0 Jumps to the Fore in 2019

2019 will be a big year for PCIe. With the approval of version 0.9 of the Base Layer for PCIe 5.0, implementers have a solid foundation to begin working on designs. PCIe 4.0 was introduced in 2017, before that the previous PCIe 3.0 was introduced in 2010 – ages ago in this industry. In fact, 5.0 is so close on the heels of 4.0, many products… Read More

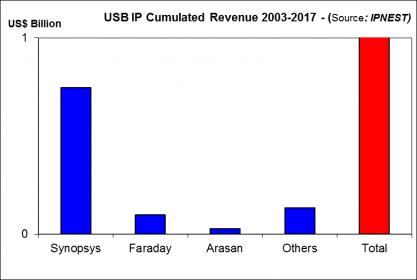

USB 3.x IP Revenue Have Grown by 31% in 2017 (IPnest)

Despite the strong consolidation in the semiconductor industry, the Design IP market is going well, very well with YoY growth of 12%+ in 2017, according with the “Design IP Report” from IPnest. If we look at the Interface IP category (20% growth in 2017) and analyze the IP revenues by protocols, we can see that USB IP is amazingly healthy,… Read More

The Importance of Daughter Cards in FPGA Prototyping

FPGA Prototyping started with the advent of FPGAs in the 1980s and today it is a fast growing market segment due to increasing chip and IP complexities up against tightening windows of opportunities. Getting your design verified quickly and allowing hardware and software engineers the opportunity to develop, test, and optimize… Read More

Intel Based FPGA Prototyping Webinar Replay

Due to the overwhelming response, here is the first part of the webinar that I did with S2C and a link to the replay. Richard Chang, Vice President of Engineering at S2C did the technical part of the webinar. Richard has a Masters degree in Electrical engineering from the University at Buffalo and more than 20 years experience designing… Read More