… is now 8 years old, and the money paid for this 10 engineers start-up was considered, at that time, as a “bingo” for Cascade’s funders: “In October 2004, the Company completed the acquisition of Cascade Semiconductor Solutions, Inc. (Cascade) for total upfront consideration of $15.8 million and contingent consideration of … Read More

Tag: pcie

In compliance we trust, for integration we verify

So, you dropped that piece of complex IP you just licensed into an SoC design, and now it is time to fire up the simulator. How do you verify that it actually works in your design? If you didn’t get verification IP (VIP) with the functional IP, it might be a really long day.

Compliance checking something like a PCIe interface block is a … Read More

New PCI Express 3.0 Equalization Requirements

PCI Express 3.0 increased the supported data rate to 8 Gbps, which effectively doubles the data rate supported by PCI Express 2.0. While the data rate was increased, no improvement was made to the channels. As such, an 8 Gbps channel in PCIe 3.0 experiences significantly more loss than one implemented in PCIe 2.0. To compensate for… Read More

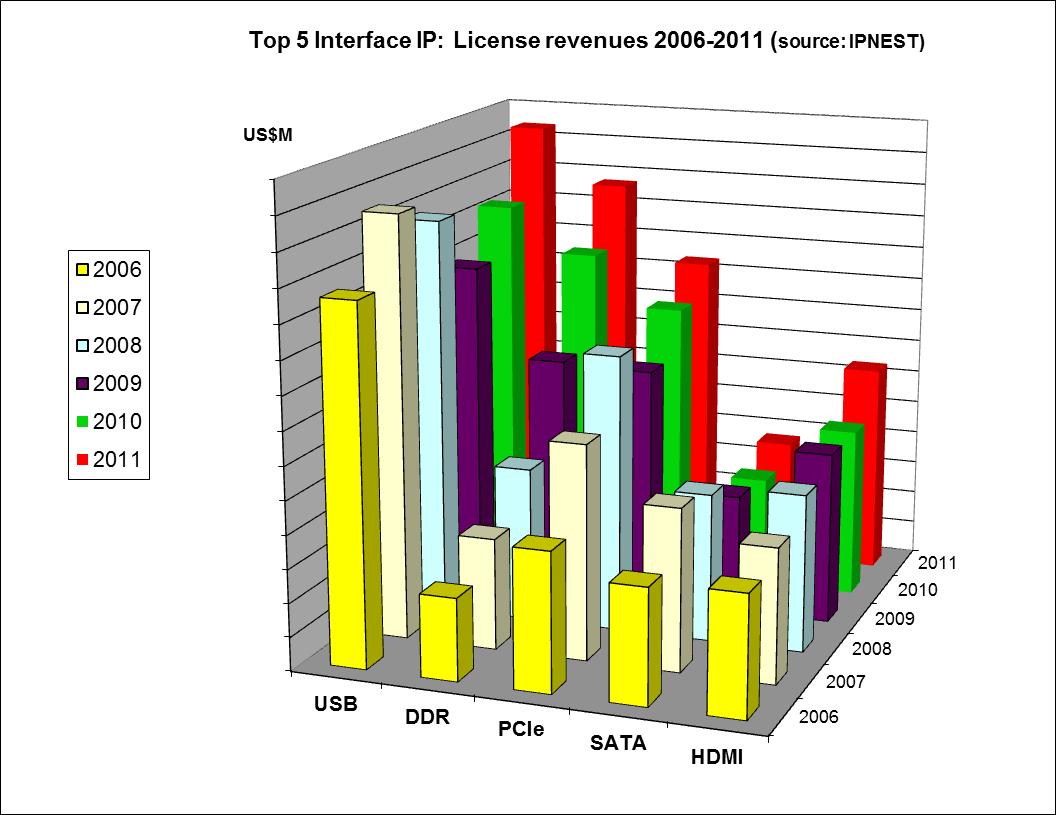

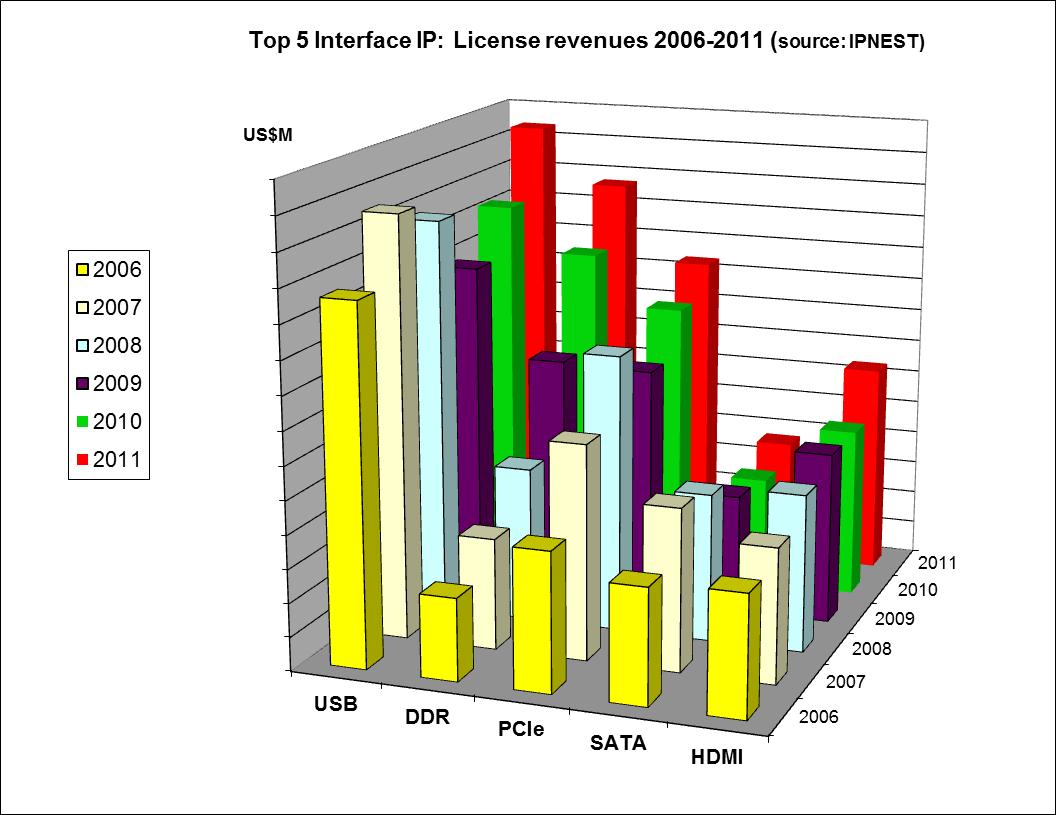

Interface Protocols, USB3, PCI Express, MIPI, SATA… the winners and losers in 2012

Who makes the decision and declare that a specific interface protocol is successful? Not me, as I can only consolidate market share data and some insight information coming from the industry. The end user, when going to a shop (real or virtual) and spend a significant part of his budget to buy an electronic product, selecting among… Read More

PCI express WILL be used in Smartphone and Media Tablet… opening infinity of new opportunities

Looking at the various Interface protocols like HDMI, SuperSpeed USB, Universal Flash Storage (UFS) or even SATA integrated in Application Processor for smartphone and media tablet, one extremely powerful Interface protocol, already in use in electronic systems from various market segments from PC, PC Peripherals, Networking,… Read More

Interface IP (USB, PCIe, SATA, HDMI, MIPI, DDRn,…) Survey : the Introduction

The need to exchange larger and larger amount of data from system to the external world, or internally into an application, has pushed for the standardization of interconnect protocol. This allows interconnecting different Integrated Circuits (IC) coming from different vendors. Some protocols have been defined to best fit… Read More

A brief history of Interface IP, the 4th version of IPNEST Survey

The industry is moving extremely fast to change the “old” way to interconnect devices using parallel bus, to the most efficient approach based on High Speed Serial Interconnect (HSSI) protocols. The use of HSSI has become the preferred solution compared with the use of parallel busses for new products developed … Read More

Shorter, better and easier PCIe and NVM Express Verification flow with advanced technologies

We have talked about Cadence subsystem IP strategy, illustrated by NVM Express subsystem IP, in a previous blog. What we said was that “A subsystem IP based approach will also speed up the software development and validation phase: if the IP provider is able to propose the right tools, like the associated Verification IP (VIP), … Read More

Such a small piece of Silicon, so strategic PHY IP

How could I talk about the various Interface protocols (PCIe, USB, MIPI, DDRn…) from an IP perspective and miss the PHY IP! Especially these days, where the PHY IP market has been seriously shaken, as we will see in this post, and will probably continue to be shaken… but we will have to wait and look at the M&A news during the next … Read More

NVM Express: pervasion of PCI Express in SSD based storage

The verification IP (VIP) for Non-Volatile Memory Express (NVMe) announcement from Synopsys is the first fruit issued from the acquisition of ExpertIO. With the proliferation of Nand Flash based storage equipment, or Solid State Drives (SSD), the move from pure SATA based solution was to be expected, sooner or later. Not because… Read More