If your company develops Design IP to support well-known protocols like USB, PCIe, HDMI, DDRn memory controller, MIPI specification (and more), it’s crucial to know your competition, the market size by segment, and even more important the market potential by segment. The latest can be obtained by the Compound Annual Growth Rate… Read More

Tag: pcie

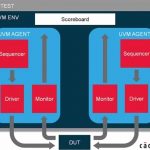

So Easy To Learn VIP Integration into UVM Environment

It goes without saying that VIPs really play a Very Important Part in SoC verification today. It has created a significant semiconductor market segment in the fabless world of SoC and IP design & verification. In order to meet the aggressive time-to-market for IPs and SoCs, it’s imperative that readymade VIPs which are proven… Read More

Synopsys Galaxy Platform & Lynx Design System supports FD-SOI

This is a new brick that Synopsys brings to build FD-SOI credibility. We have talked at Semiwiki about FD-SOI technology developed by the LETI and STM, and recently endorsed by Samsung Foundry, offering a more than credible second source to STM. And we have said that the FD-SOI introduction will need to be supported by EDA and IP vendors… Read More

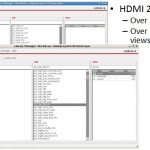

High Quality PHY IPs Require Careful Management of Design Data and Processes

In last few years IP design has grown significantly compared to the rest of the semiconductor industry. There are newer IP start-ups opening across the world, particularly in India and China. Amid this rush, I wanted to understand the actual dynamics pushing this business and whether all of these IPs follow quality standards. … Read More

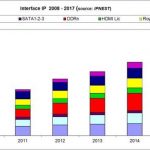

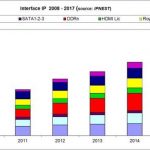

What’s new in the “Interface IP Survey” ?

The reader will find many updates in the “Interface IP Survey” from IPNEST, released in October 2013. Good question, as the IP market is a very fast moving one and the protocol based Interface IP, is moving even faster… exhibiting 20% growth rate in 2012, expected to grow with 10% CAGR between 2012 and 2017 to reach $700M. … Read More

Interface Protocols, USB3, PCI Express, MIPI, DDRn… the winner and losers in 2013

How to best forecast a specific protocol adoption? One option is to look at the various IP sales, it will give you a good idea of the number of SoC or IC offering this feature on the market in the next 12 months. Once again, if you wait for the IP sale to have reached a maximum, it will be too late, so you have to monitor the IP sales dynamic when… Read More

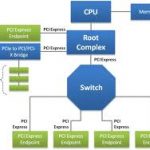

Mobile SoC will benefit now from M-PCIe

We have already discussed the recently released M-PCIe ECN from PCI-SIG in Semiwiki at the end of 2012, but the new “standard” (in fact an Engineering Change from PCI-SIG and MIPI Alliance) was only real on paper, at that time. The upcoming webinar from Synopsys, M-PCIe: Utilizing Low-Power PCI Express in Mobile Designs, shows … Read More

The FPGA Blob is Coming…

I never understood when I was a kid how ‘the Blob’ could actually catch someone but it sure did. It caught the unsuspecting, the off guard. I mean you’d have time for a soda and shower if you saw it on your road. And no, your manager is not the Blob; don’t think like that, it’s always his boss. The blob comes to consume the worker who was unaware… Read More

Data Centers accounts for 2 to 3% of WW Energy Consumption!

Do you think this figure will go down? Considering the massive move to Mobile equipment, pushing to de-localize your storage medium to instead use the cloud capabilities, and looking at the huge number of people buying smartphone and tablet in emerging countries, no doubt that Data Center related energy consumption is expected… Read More

Are you going to the plug fest?

PCI Express 3.0 specification is 1000 pages long. Most of us, and most of the designers integrating PCIe gen-3 into their latest ASIC, FPGA or system will probably never read it completely, or even open it. In fact, they don’t need to read it completely, but they should care about one point, whether they buy an ASSP or a PCIe design IP:… Read More