Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

Tag: neural networks

Intellectual Abilities of Artificial Intelligence (AI)

To understand AI’s capabilities and abilities we need to recognize the different components and subsets of AI. Terms like Neural Networks, Machine Learning (ML), and Deep Learning, need to be define and explained.

In general, Artificial intelligence (AI) refers to the simulation of human intelligence in machines that are programmed… Read More

Bigger, Faster and Better AI: Synopsys NPUs

AI-based applications are fast advancing with evolving neural network (NN) models, pushing aggressive performance envelopes. Just a few years ago, performance requirements of NN driven applications were at 1 TOPS and less. Current and future applications in the areas of augmented reality (AR), surveillance, high-end smartphones,… Read More

Embedded Logic-NVM Solutions for Al Chips

Last month, eMemory Technology hosted a webinar titled “eMemory’s Embedded Logic-NVM Solution for AI Chips.” While the purpose was to present their embedded Logic-NVM solution, the webinar nicely sets the stage by highlighting Analog NVM’s value as it relates to neural networks. Of course, the algorithms of neural networks… Read More

A No-Fudge ML Architecture for Arm

At TechCon I had a 1×1 with Steve Roddy, VP of product marketing in the Machine Learning (ML) Group at Arm. I wanted to learn more about their ML direction since I previously felt that, amid a sea of special ML architectures from everyone else, they were somewhat fudging their position in this space. What I heard earlier was that… Read More

AI Hardware Summit, Report #3: Enabling On-Device Intelligence

This is the third and final blog I have written about the recent AI Hardware Summit held at the Computer History Museum in Mountain View, CA. Day 1 of the conference was more about solutions in the data center, whereas Day 2 was primarily around solutions at the Edge. This presentation from Day 2 was given by Dr. Thomas Anderson, Head,… Read More

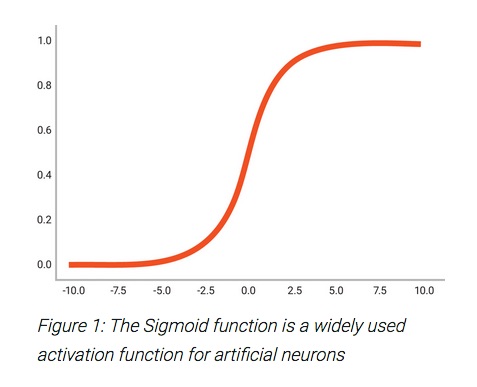

Mathematics are Hard – That is Why AI Needs Mathematics Hardware

The field of artificial intelligence has relied on heavy inspiration from the world of natural intelligence, such as the human mind, to build working systems that can learn and act on new information based on that learning. In natural networks, neurons do the work, deciding when to fire based on huge numbers of inputs. The relationship… Read More

AI processing requirements reveal weaknesses in current methods

The traditional ways of boosting computing throughput are either to increase operating frequency or to use multiprocessing. The industry has done a good job of applying these techniques to maintain a steady increase in performance. However, there is a discontinuity in the needs for processing power. Artificial Intelligence… Read More

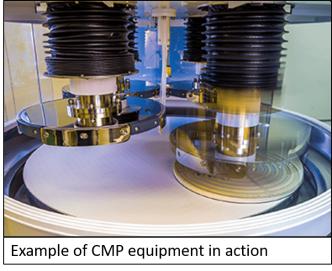

Mentor Investigates Using Neural Networks for CMP Modeling

I recently read a new white paper release by Mentor, a Siemens Business, that delved into the intricacies of Chemical Mechanical Polishing (CMP) and I got a sense of Déjà vu. My professional career in the IC industry started at Texas instruments and the white paper made me think of a conversation I had with one of my colleagues over … Read More

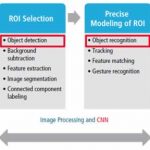

Cadence loads up on MACs for vision with CNNs

For vision DSP IP running convolutional neural networks (CNNs), a big driver of performance is increasing the bits processed per cycle with parallel MACs. Tom Simon did a great job in recent posts of introducing CNNs at a high level, so I’ll look at what is architecturally behind Cadence’s latest announcement: the Tensilica Vision… Read More