The internet keeps adding users and connected devices. According to the numbers in a white paper from Achronix, by 2022 there will be 4.8 billion internet users and 28.5 billion connected devices. Internet traffic will reach 275 exabytes per month. Of this a staggering 83 percent will be video traffic. Moving the data from creators… Read More

Tag: network on chip

Interconnect Basics: Wires to Crossbar to NoC

To many of us, if we ever think about interconnect on an SoC, we may think delay, power consumption, congestion, that sort of thing. All important points from an implementation point of view, but what about the functional and system implications? In the early days, interconnect was very democratic, all wires more or less equal, … Read More

Webinar – FPGA Native Block Floating Point for Optimizing AI/ML Workloads

Block floating point (BFP) has been around for a while but is just now starting to be seen as a very useful technique for performing machine learning operations. It’s worth pointing out up front that bfloat is not the same thing. BFP combines the efficiency of fixed point operations and also offers the dynamic range of full floating… Read More

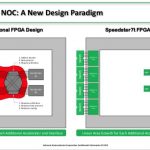

Network on Chip Brings Big Benefits to FPGAs

The conventional thinking about programmable solutions such as FPGAs is that you have to be willing to make a lot of trade-offs for their flexibility. This has certainly been the case in many instances. Even just getting data across the chip can eat up valuable routing resources and add a lot of overhead. These problems are exacerbated… Read More

Free webinar – Accelerating data processing with FPGA fabrics and NoCs

FPGAs have always been a great way to add performance to a system. They are capable of parallel processing and have the added bonus of reprogramability. Achronix has helped boost their utility by offering on-chip embedded FPGA fabric for integration into SoCs. This has had the effect of boosting data rates through these systems… Read More

An evolution in FPGAs

Why does it seem like current FPGA devices work very much like the original telephone systems with exchanges where workers connected calls using cords and plugs? Achronix thinks it is now time to jettison Switch Blocks and adopt a new approach. Their motivation is to improve the suitability of FPGAs to machine learning applications,… Read More

Leveraging AI to help build AI SOCs

When I first started working in the semiconductor industry back in 1982, I realized that there was a race going on between the complexity of the system being designed and the capabilities of the technology in the tools and systems used to design them. The technology used to design the next generation of hardware was always lagging… Read More

Artificial Intelligence calls for Smart Interconnect

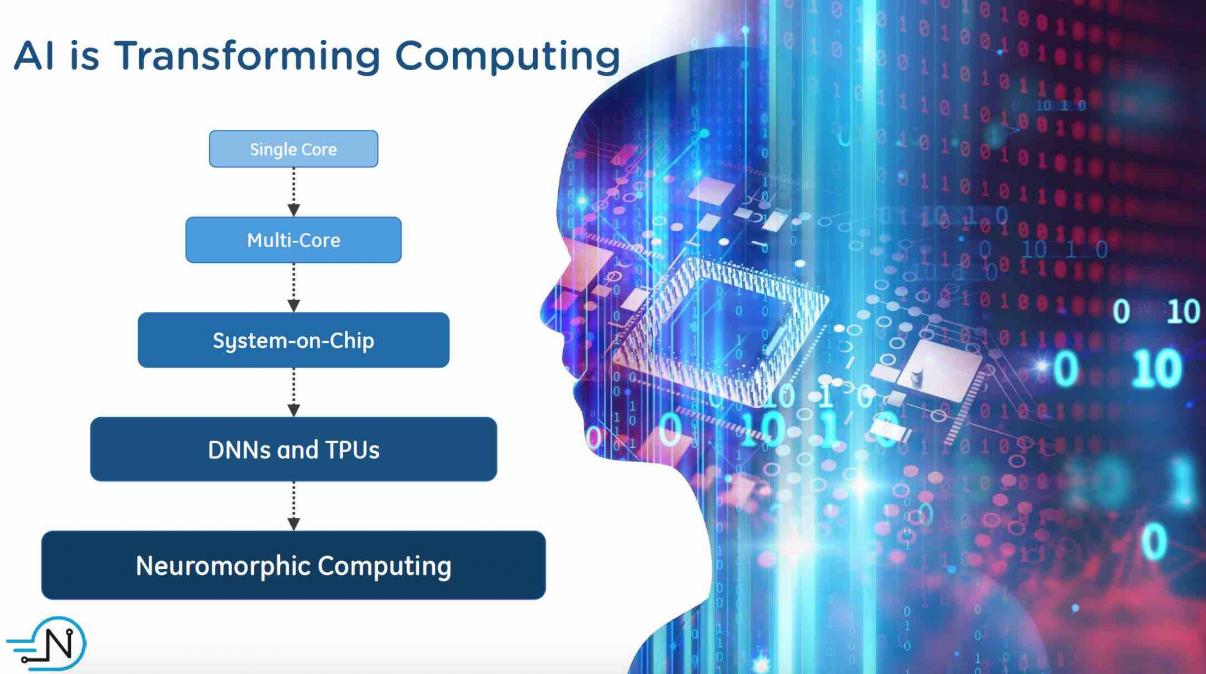

Artificial Intelligence based systems are driving a metamorphosis in computing, and consequently precipitating a large shift in SOC design. AI training is often done in the cloud and has requirements for handling huge amounts of data with forward and backward data connections. Inference usually occurs at the edge and must be… Read More

AI Based Software Designing AI Based Hardware – Autonomous Automotive SoC Platform

For those of you who missed the NetSpeed Systems, Imagination Technologies webinar, “Alexa, can you help me build a better SoC”, you’ll be happy to hear that the session was recorded and can still be viewed (see link at the bottom of this page). I’ll warn you now however, that this was a high-bandwidth session packed with information,… Read More

Automotive System Reliability – ISO 26262 impacts IP and Tools

If you have been following the topic of ISO 26262, you now realize that IP, or even EDA design tools, developed with the highest quality standards still can’t be ISO 26262 certified. Recently I had a conversation with Kurt Shuler from Arteris about this topic. He is VP of Marketing at Arteris, and he is also on several ISO 26262 technical… Read More