The most vexing problem for physical implementation engineers is debugging errors due to power-ground “shorts”, as reported by the layout-versus-schematic (LVS) physical verification flow. The number of polygons associated with each individual grid is large – an erroneous connection between grids results in a huge number… Read More

Tag: mentor

Mentor Offers Next Generation DFT with Streaming Scan Network

Design for test (DFT) requires a lot of up-front planning that can be difficult to alter if testing needs or performance differ from initial expectations. Hierarchical methodologies help in many ways including making it easier to reduce on chip resources such as the number of test signals. Also, hierarchical test allows for speed-ups… Read More

How About a Faster Fast SPICE? Much Faster!

When Analog FastSPICE was first introduced in 2006 it changed the landscape for high performance SPICE simulation. During the last 14 years it has been used widely to verify advanced nanometer designs. Of course, since then the most advanced designs have progressed significantly, making verification even more difficult. Just… Read More

The Moving Target Known as UPF

As if engineers did not have enough difficulty just getting everything right so that their designs are implemented functionally correct, the demands of lowering power consumption require changes that can affect functionality and verification. Techniques such as power gating, clock gating, mixed supply voltage, voltage … Read More

High Speed SerDes Design and Simulation Webinar Replay from Mentor

Over the years SerDes (serializer/deserializer) based connections have proliferated into just about every connection within and among computing systems. Years ago, parallel interfaces were the most common method of moving data, but issues of signal integrity, synchronization and power simply became too much for the required… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

Learning to Live with the Gaps Between Design and Verification

Whenever I am asked to explain how chip design works by someone who is unfamiliar with the process, I struggle to explain the different steps in the flow. It also makes me aware of the discrete separations between each phase of activities. Of course, when you speak to a novice it is not even possible to get more than one layer down in the… Read More

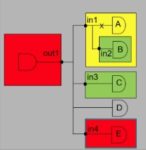

Bringing Hierarchy to DFT

Hierarchy is nearly universally used in the SoC design process to help manage complexity. Dealing with flat logical or physical designs proved unworkable decades ago. However, there were a few places in the flow where flat tools continued to be used. Mentor lead the pack in the years around 1999 in helping the industry move from … Read More

Photonics Come into Focus: 2020 Predictions

In the past, I’ve focused my annual predictions on electronics – ICs and EDA – but recently I’ve turned my focus to photonics, so my 2020 predictions are primarily in this area.

Historically, photonics has been the Gallium Arsenide of technologies; it was, is and always will be the technology of the future. Analysts have forever … Read More

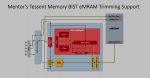

Full Solution for eMRAM Coming in 2020

It’s amazing to think that Apollo moon mission used computers that were based on magnetic core memories. Of course, CMOS memories superseded them rapidly. However, over the decades since, memory technologies have advanced significantly, in terms of density, power and new types of technologies, e.g NAND Flash. Ever since the… Read More