You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

One year ago activist investor Carl Icahn started a hostile takeover bid for Mentor Graphics and was able to offer up three new board members, however yesterday we read that Mentor Graphics will:

- Have their annual shareholder meeting on May 30th

- Two of Icahn’s board members are not on the roster for renewal

- Mr. Icahn has no

…

Read More

IC device physics uncovers limits to reliable operation, so IC designers are learning to first identify and then fix reliability issues prior to tape-out. Here’ s a list of reliability issues to keep you awake at night:… Read More

Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly … Read More

Conquering the Big Data Challengesby Beth Martin on 04-02-2012 at 4:38 pmCategories: EDA, Siemens EDA

Extrapolating the trends from last 20 years to the next ten suggests that we will be implementing a trillion transistors or more by 2020. At 20nm, with the chip sizes touching billions of transistors, the age old problem of how to implement a design in the most efficient manner remains unanswered. … Read More

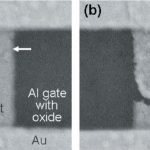

My first chip design at Intel was a DRAM and we had a 5% yield problem caused by electromigration issues, yes, you can have EM issues even with 6um NMOS technology. We had lots of questions but precious few answers on how to pinpoint and eliminate the source of yield loss. Fortunately, with the next generation of DRAM quickly introduced… Read More

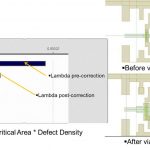

Although design for manufacturing (DFM) tools and techniques have been around for several nodes, a lot of designers remain skeptical about their actual value, especially since many products still make it successfully to market without the use of DFM.… Read More

DFM at SPIE Advance Litho showby Beth Martin on 02-09-2012 at 6:40 pmCategories: EDA, Siemens EDA

This year’s SPIE Advanced Lithography is loaded with interesting keynotes and sessions. To help me narrow down what to see, I spoke with John Sturtevant. John is co-chair of the Design for Manufacturability through Design-Process Integration conference, and the director for technical marketing for RET products at Mentor Graphics.… Read More

Consumer electronics is a new driver in our global semiconductor economy as we enjoy using Smart Phones, Tablets and Ultra Books. The challenge of designing and then verifying the electronic systems to meet the market windows is a daunting one. Instead of starting with a blank sheet for a new product, most electronic design companies… Read More

For the greater good of the semiconductor ecosystem, SemiWiki and Mentor Graphics present SemiWiki Seminars, a free seminar and software demonstration series addressing the latest innovations in IC design. SemiWiki Seminars discuss interesting new challenges and potential solutions aimed at increased circuit density … Read More

Hierarchy is used in IC designs at many abstraction levels to help describe a design in a compact format:

- Mask Data

- IC Layout

- Schematic Netlists

- Gate level netlists

- RTL netlists

But the question and focus for this blog is, “What is a hierarchical SPICE Circuit Simulator?”… Read More