Rarely does a month go by without acquisitions in the fabless semiconductor ecosystem. Not surprisingly one of the most read pages on SemiWiki is the EDA Merger and Acquisitions Wiki with more than fifty seven thousand views. It really is a nice family tree, one which we (Daniel Payne) are diligent on keeping current. One of the most… Read More

Tag: mentor graphics

Congratulations Dr. Walden C. Rhines!

A funny thing happened at the Design Automation Conference last June in San Francisco. I was browsing the Kaufman award winner mug shots in the EDAC booth and noticed that Wally Rhines was NOT a winner. You can see them HERE. Immediately in disbelief I said to myself: Self, how can this be? Joe Costello, Aart de Geus, and some other guys… Read More

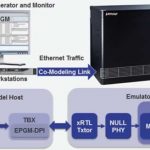

Testing Ethernet with virtual co-modeling

Ethernet is suddenly a hot topic in SoC design again. The biggest news may be this: it’s not just the cloud and enterprise networks. Those are still important applications. The cloud is driving hard for more ports at 25G server and 100G switch speeds according to a recent Dell’Oro Group report. Enterprise networks are driving for… Read More

Mentor 2Q Results

So it was Mentor’s turn yesterday after Synopsys on Wednesday. And yes, it really is the end of their second quarter. They produced some very good results. As Wally opened:The second quarter of fiscal 2016 was one of record for Q2. We substantially exceed our own expectations was revenue of $281.1 million and non-GAAP earnings… Read More

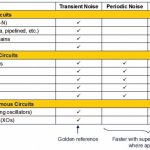

Device Noise Analysis, What Not to Do for AMS IC Designs

AMS IC designers have a lot to think about when crafting transistor-level designs to meet specifications and schedules, so the most-used tool in their kit is the trusted SPICE or FastSPICE circuit simulator to help analyze timing, power, sensitivity and even device noise. I just did a Google search for “device noise analysis… Read More

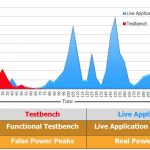

Getting the Best Dynamic Power Analysis Numbers

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

Ask me about Mentor at DAC!

If you’ve been following DAC general chair Anne Cirkel’s weekly blog, you know the conference program is now final. There’s much to suggest it will be a great DAC, including a record number of submissions in several content categories and a compelling lineup of keynoters. The week will start with an update on Google’s smart contact… Read More

TSMC 10nm Readiness and 3DIC

At the TSMC Technology Symposium last month Suk Lee presented a lot of information on design enablement. Suk is an interesting guy with a unique background in ASIC, Semiconductor, EDA, and now Foundry. In baseball terms that would be like playing infield, outfield, home plate, and umpire!

Around the turn of the millennium Suk actually… Read More

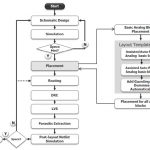

Can You Really Automate Analog IC Layout?

Digital IC design has been largely automated with high-level languages, RTL coding, logic synthesis, and automated place and route tools. What about analog IC layout automation, is it possible? A few EDA companies think that it is possible and even practical. In recent memory there were two companies really focused on analog … Read More

Advances in Nanometer Analog and Mixed Signal Design!

Mentor’s annual user group meeting at the Doubletree Hotel in San Jose, CA is coming up on Tuesday, April 21[SUP]st[/SUP]. This complementary event provides a unique opportunity to share design techniques and exchange ideas with other users and experts in the design community. As you may have read I am the star of the show; moderating… Read More